Texas Instruments MSP430x1xx User Manual

Page 195

Timer Modes

11-19

Timer_B

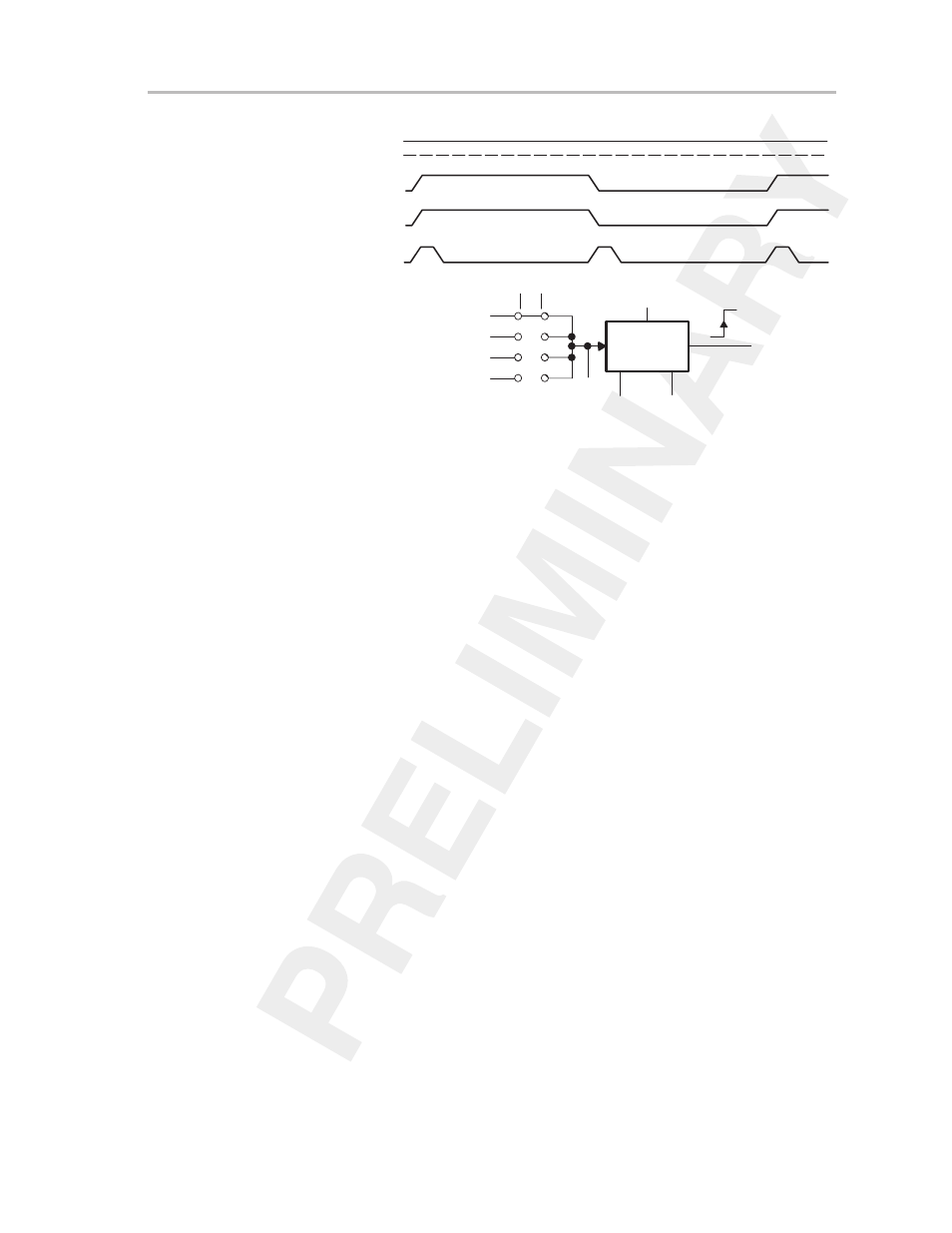

Figure 11–21.Software Capture Example

Capture

Mode

CCISx0

CCISx1

CCIxA

CCIxB

GND

0

1

2

3

V

CC

CCMx1 CCMx0

CMPx

CCIx

CCISx1

CCISx0

CCIx

Capture

Capture

Both Edges Selected

1

1

The following is a software example of a capture performed by software:

; The data of capture/compare register CCRx are taken

; by the software. It is assumed that CCMx1, CCMx0, and

; CCISx1 bits are set. Bit CCIS0 selects the CCIx

; signal to be high or low.

;

;

...

...

XOR

#CCISx0, &CCTLx

...

...

...

11.4.2 Capture/Compare Block—Compare Mode

The compare mode is selected if the CAPx bit, located in control word CCTLx,

is reset. In compare mode all the capture hardware circuitry is inactive and the

capture-mode overflow logic is inactive.

The compare mode is most often used to generate interrupts at specific time

intervals or used in conjunction with the output unit to generate output signals

such as PWM signals.

The compare data is double-buffered. The software writes the compare data

to the capture/compare register, but the data is transferred to the compare

latch TBCLx to be compared by the compare logic. The transfer of the compare

data from the CCRx register to the compare latch is user-selectable to be

either immediate or dependent upon a timer event. This double buffering

allows the user to update multiple compare values simultaneously. This is

useful for example with PWM signals where the period or duty cycle of multiple

signals needs to be updated simultaneously. See section 11.4.2.1 for more

discussion on how to use and configure the compare latches.

If the timer becomes equal to the value in compare latch TBCLx, then: