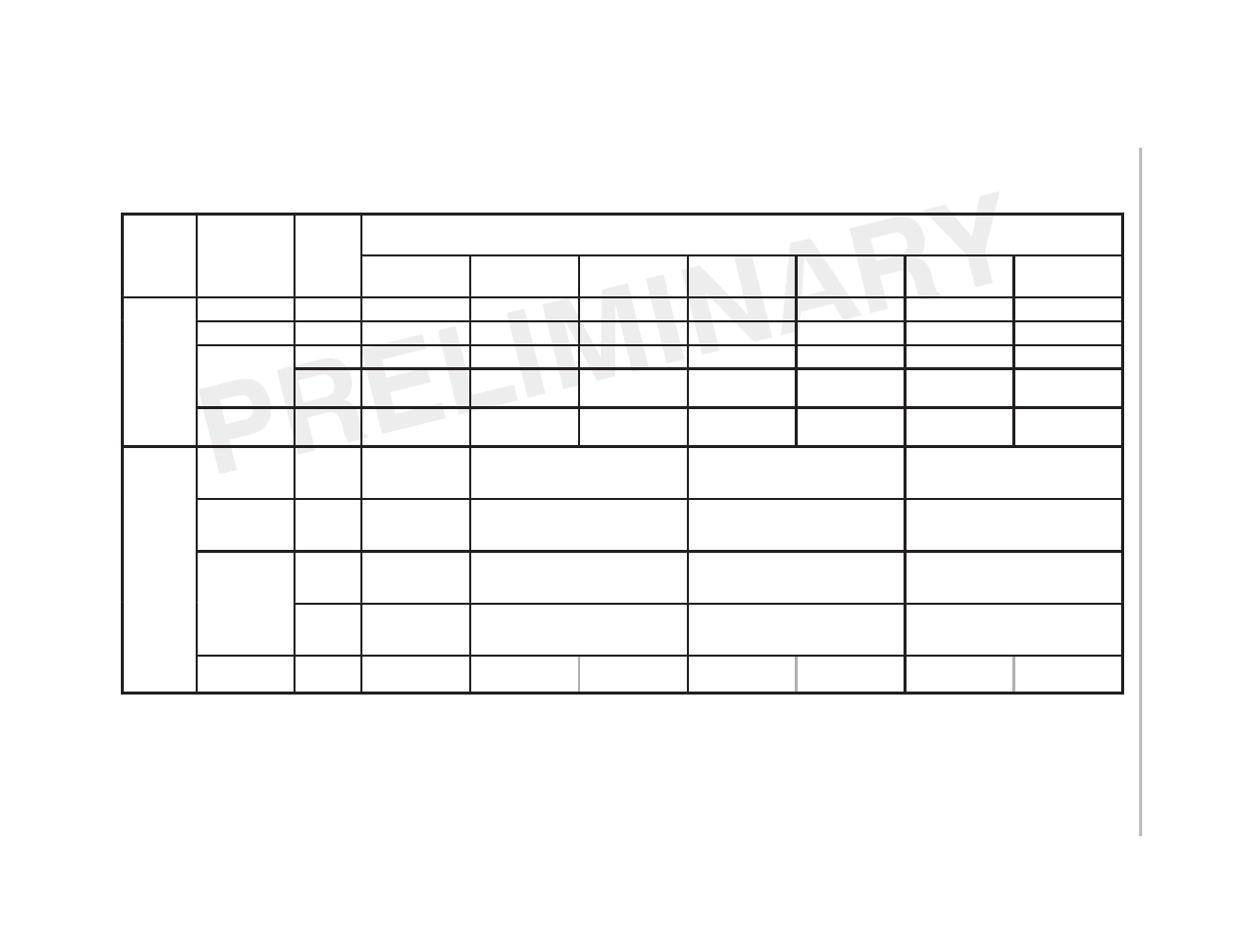

Table 11–2. shadow register operating modes – Texas Instruments MSP430x1xx User Manual

Page 197

T

imer Modes

1

1-21

T

imer_B

The groupings and load conditions are summarized below in Table 11–2

Table 11–2. Shadow Register Operating Modes

TBCLGRP

CLLDx From

Lowest

CCTLx in

Counter

Mode

Load Conditions

TBCLGRP

CCTLx in

Group (see

Note 1)

Mode

MCx

0

1

2

3

4

5

6

0

0–3

Immediate

Immediate

Immediate

Immediate

Immediate

Immediate

Immediate

1

1–3

TBR counts to 0

TBR counts to 0

TBR counts to 0

TBR counts to 0

TBR counts to 0

TBR counts to 0

TBR counts to 0

0

1,2

TBR counts to 0

TBR counts to 0

TBR counts to 0

TBR counts to 0

TBR counts to 0

TBR counts to 0

TBR counts to 0

0

2

3

TBR counts to 0

or to TBCL0

TBR counts to 0

or to TBCL0

TBR counts to 0

or to TBCL0

TBR counts to 0

or to TBCL0

TBR counts to 0

or to TBCL0

TBR counts to 0

or to TBCL0

TBR counts to 0

or to TBCL0

3

1–3

TBR counts to

TBCL0

TBR counts to

TBCL1

TBR counts to

TBCL2

TBR counts to

TBCL3

TBR counts to

TBCL4

TBR counts to

TBCL5

TBR counts to

TBCL6

0

0–3

Immediate

TBCL1, TBCL2 loaded immediately

when the corresponding CCRx

register is loaded

TBCL3, TBCL4 loaded immediately

when the corresponding CCRx

register is loaded

TBCL5, TBCL6 loaded immediately

when the corresponding CCRx

register is loaded

1

1–3

TBR counts to 0

TBCL1, TBCL2 updated

simultaneously when TBR counts

to 0

TBCL3, TBCL4 updated

simultaneously when TBR counts

to 0

TBCL5, TBCL6 updated

simultaneously when TBR counts

to 0

1

2

1,2

TBR counts to 0

TBCL1, TBCL2 updated

simultaneously when TBR

counts to 0

TBCL3, TBCL4 updated

simultaneously when

TBR counts to 0

TBCL5, TBCL6 updated

simultaneously when

TBR counts to 0

2

3

TBR counts to 0

or to TBCL0

TBCL1, TBCL2 updated

simultaneously when TBR counts to

0 or to TBCL0

TBCL3, TBCL4 updated

simultaneously when TBR counts to

0 or to TBCL0

TBCL5, TBCL6 updated

simultaneously when TBR counts to

0 or to TBCL0

3

1–3

TBR counts to

TBCL0

TBR counts to

TBCL1

TBR counts to

TBCL2

TBR counts to

TBCL3

TBR counts to

TBCL4

TBR counts to

TBCL5

TBR counts to

TBCL6