7 sampling, Figure 15–14. the sample-and-hold function, 1 sampling operation – Texas Instruments MSP430x1xx User Manual

Page 312: 13 × (adc12div/f

Sampling

15-22

The conversion starts with the falling edge of the sample signal SAMPCON

(see the

Sampling section and Figure 15–14). Thirteen conversion clocks

(ADC12CLK) are required to complete a conversion. The conversion time is:

t

conversion

= 13

×

(ADC12DIV/f

ADC12CLK

)

Where ADC12DIV is any integer from 1 to 8. The ADC12CLK frequency must

not exceed the maximum and minimum frequencies specified in the data

sheet. Either violation may result in inaccurate conversion results.

Note:

Availability of ADC12CLK During Conversion

Users must ensure that the clock chosen for ADC12CLK remains active

until the ADC12 can complete its operation. If the clock is removed

while the ADC12 is active, the operation can not be completed and the

end-of-conversion feedback to the program is not possible.

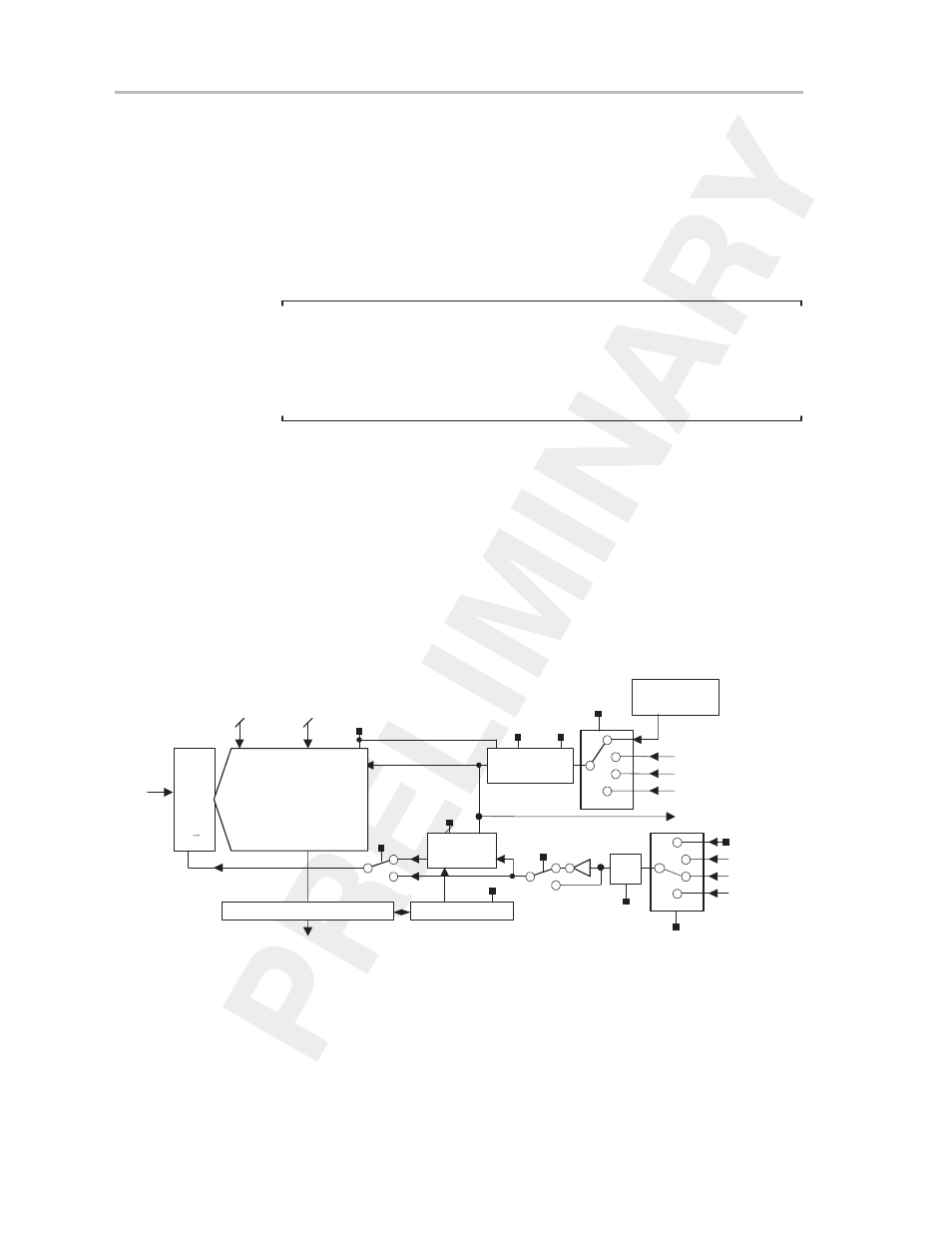

15.7 Sampling

The ADC12 sample-and-hold (S/H) circuitry (shown in Figure 15–14) is flex-

ible and configurable. The configuration is done by software via control bits in

the ADC12CTL0 and ADC12CTL1 registers. Configuration and operation of

the S/H circuitry is discussed in this section.

Figure 15–14. The Sample-and-Hold Function

ACLK

MCLK

SMCLK

ADC12OSC

Internal

Oscillator

ADC12CLK

S/H

Divide by

1,2,3,4,5,6,7,8

Sampling

Timer

12–bit S A R

ADC12DIV

ISSH

SHP

SHT1

SHT0

ADC12ON

ADC12SSEL

12–bit A/D converter core

analog

input

signal

Conversion CTL

MSC

SAMPCON

SHI

SHS

ENC

ADC12SC

Timer_A.OUT1

Timer_B.OUT0

Timer_B.OUT1

SYNC

VR–

VR+

Sample

Hold

and

15.7.1 Sampling Operation

The sample-and-hold circuitry samples the analog signal when the sampling

signal SAMPCON (see Figure 15–14) is high. Conversion starts immediately

with the falling edge of SAMPCON. The sample-and-hold holds the signal

value when SAMPCON is low. Conversion takes 13 ADC12CLK cycles (see

Figure 15–15).