3 capture/compare control register cctlx – Texas Instruments MSP430x1xx User Manual

Page 167

Timer_A Registers

10-27

Timer_A

Note:

Modifying Timer A Register TAR

When ACLK, SMCLK, or the external clock TACLK or INCLK is selected for

the timer clock, any write to timer register TAR should occur while the timer

is not operating; otherwise, the results may be unpredictable. In this case,

the timer clock is asynchronous to the CPU clock MCLK and critical race

conditions exist.

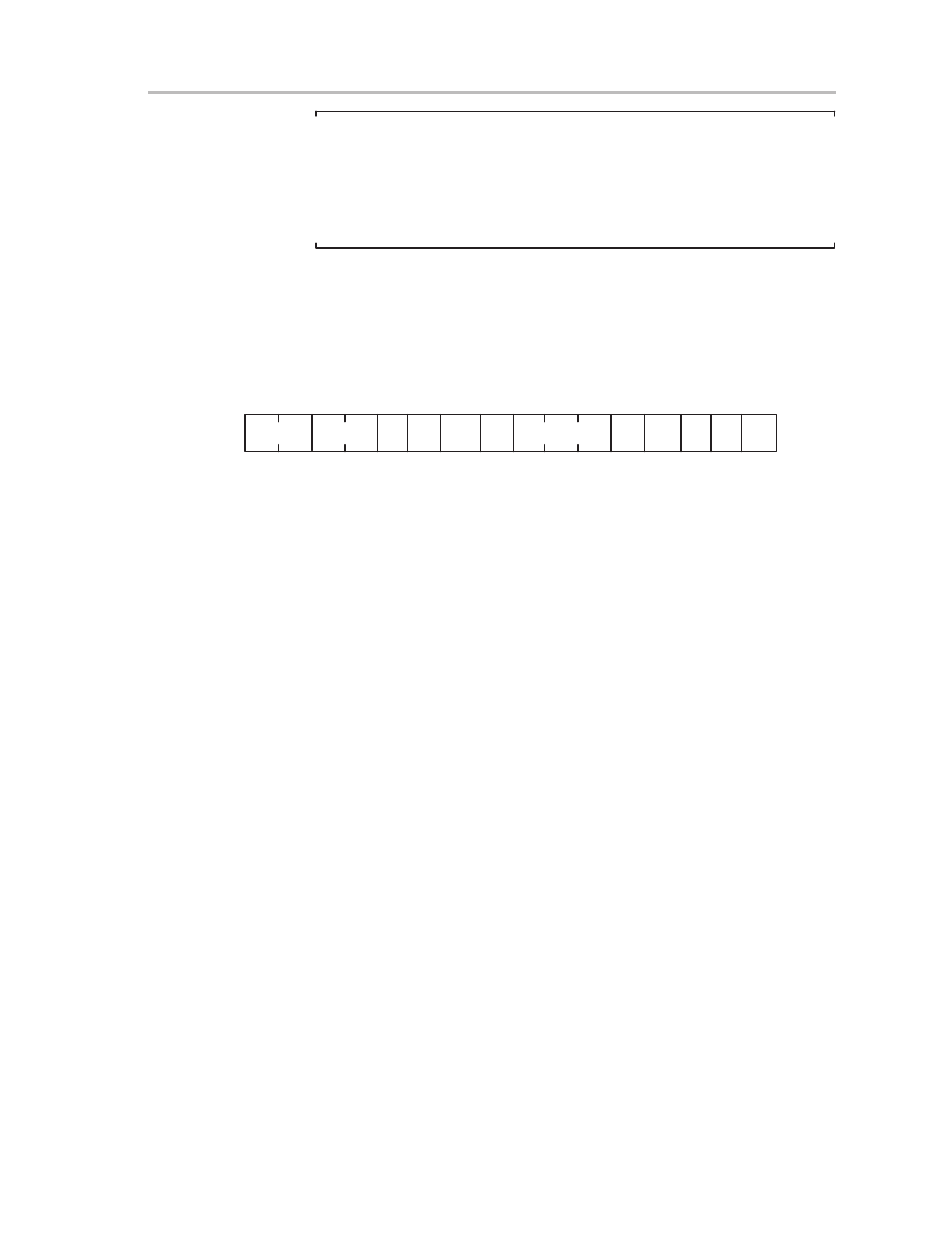

10.6.3 Capture/Compare Control Register CCTLx

Each capture/compare block has its own control word CCTLx, shown in

Figure 10–29. The POR signal resets all bits of CCTLx; the PUC signal does

not affect these bits.

Figure 10–29. Capture/Compare Control Register CCTLx

rw-(0)

15

0

Input

Select

CCIE

OUT COV CCIFG

CCTLx

162h to 16Ah

Capture

Mode

SCS SCCI Unused CAP

OUTMODx

CCI

r

rw-(0) rw-(0) rw-(0)rw-(0) rw-(0) r-(0) rw-(0)rw-(0)rw-(0)rw-(0) rw-(0)

rw-(0)rw-(0) rw-(0)

Bit 0:

Capture/compare interrupt flag CCIFGx

Capture mode:

If set, it indicates that a timer value was captured in the

CCRx register.

Compare mode:

If set, it indicates that a timer value was equal to the data

in the CCRx register.

CCIFG0 flag:

CCIFG0 is automatically reset when the interrupt request

is accepted.

CCIFG1 to CCIFG4 flags:

The flag that caused the interrupt is automatically reset

after the TAIV word is accessed. If the TAIV register is not

accessed, the flags must be reset with software.

No interrupt is generated if the corresponding interrupt

enable bit is reset, but the flag will be set. In this scenario,

the flag must be reset by the software.

Setting the CCIFGx flag with software will request an

interrupt if the interrupt-enable bit is set.

Bit 1:

Capture overflow flag COV

Compare mode selected, CAP = 0:

Capture signal generation is reset. No compare event will

set COV bit.

Capture mode selected, CAP = 1:

The overflow flag COV is set if a second capture is

performed before the first capture value is read. The

overflow flag must be reset with software. It is not reset by

reading the capture value.

Bit 2:

The OUTx bit determines the value of the OUTx signal if the

output mode is 0.