Texas Instruments MSP430x1xx User Manual

Page 73

Addressing Modes

5-9

16-Bit CPU

5.2.2

Indexed Mode

The indexed mode is described in Table 5–6.

Table 5–6. Indexed Mode Description

Assembler Code

Content of ROM

MOV 2(R5),6(R6)

MOV X(R5),Y(R6)

X = 2

Y = 6

Length:

Two or three words

Operation:

Move the contents of the source address (contents of R5 + 2)

to the destination address (contents of R6 + 6). The source

and destination registers (R5 and R6) are not affected. In

indexed mode, the program counter is incremented

automatically so that program execution continues with the

next instruction.

Comment:

Valid for source and destination

Example:

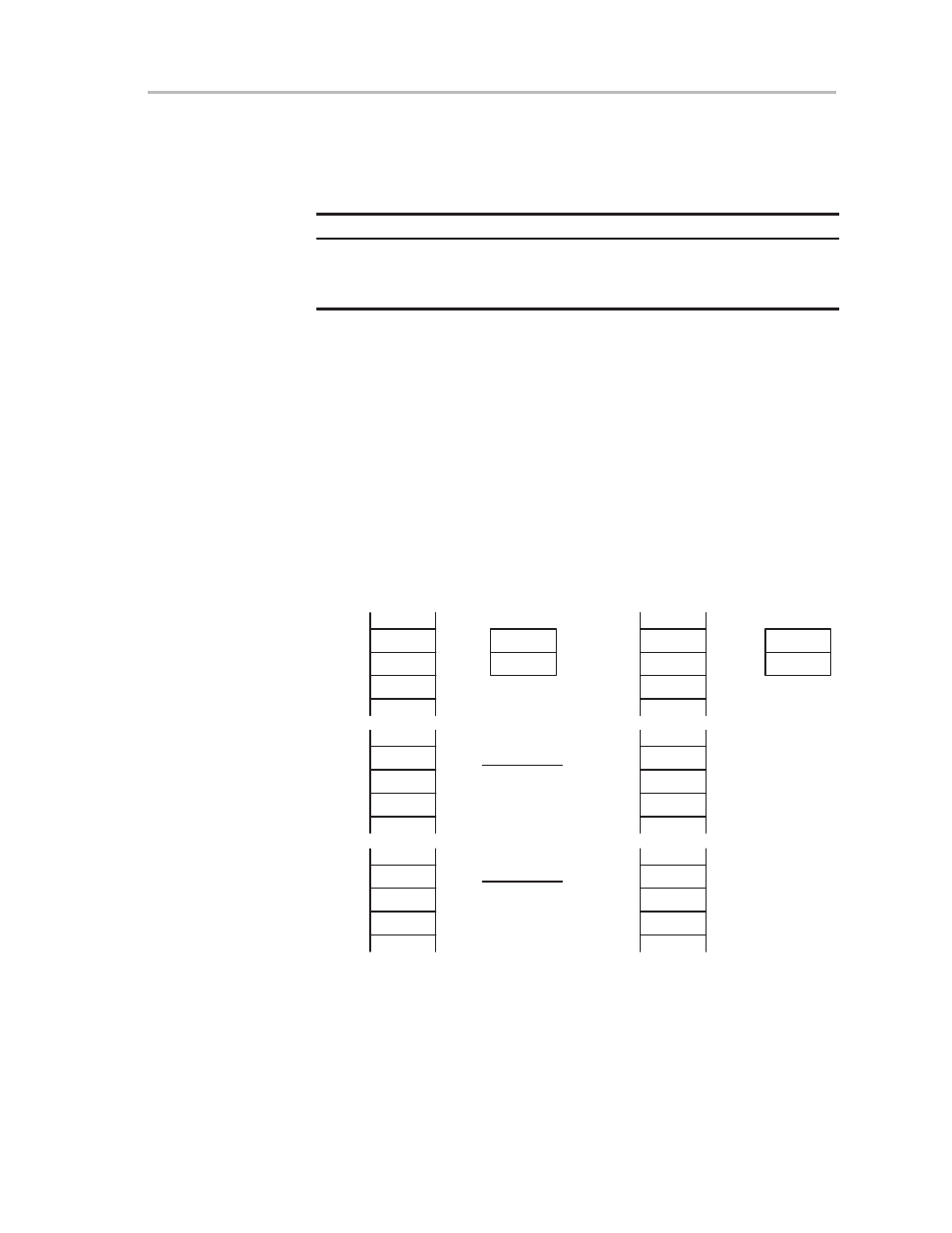

MOV 2(R5),6(R6):

00006h

Address

Space

00002h

04596h

PC

0FF16h

0FF14h

0FF12h

0xxxxh

05555h

01094h

01092h

01090h

0xxxxh

0xxxxh

01234h

01084h

01082h

01080h

0xxxxh

01080h

0108Ch

R5

R6

0108Ch

+0006h

01092h

01080h

+0002h

01082h

Register

Before:

00006h

Address

Space

00002h

04596h

PC

0FF16h

0FF14h

0FF12h

0xxxxh

01234h

01094h

01092h

01090h

0xxxxh

0xxxxh

01234h

01084h

01082h

01080h

0xxxxh

01080h

0108Ch

R5

R6

Register

After:

0xxxxh

- Digital Signal Processor SM320F2812-HT (153 pages)

- Laser And Motor Drives DRV8811EVM (13 pages)

- TMS320 DSP (88 pages)

- MSP430x11x1 (45 pages)

- TVP5154EVM (55 pages)

- TMS320DM646X DMSOC (64 pages)

- CC2511 (24 pages)

- SN65HVS880 (4 pages)

- TPS650231EVM (14 pages)

- TMS320TCI648x (256 pages)

- TSC2007EVM-PDK (16 pages)

- UCC38500EVM (16 pages)

- TMS320C6000 (62 pages)

- SCAU020 (21 pages)

- TPS40051 (17 pages)

- TNETE2201 (14 pages)

- TMS320C64x DSP (306 pages)

- UCC2891 (21 pages)

- TMS320C3x (757 pages)

- MSP430 (138 pages)

- TMS320C6712D (102 pages)

- MSP430x4xx (512 pages)

- TMS320C6454 (225 pages)

- SPRU938B (48 pages)

- TUSB3210 (22 pages)

- TMS320C6457 (43 pages)

- CC2530ZNP (3 pages)

- TMS320C6455 (50 pages)

- TSB12LV26 (91 pages)

- TMS320C6472 (2 pages)

- VLYNQ Port (49 pages)

- TMS380C26 (92 pages)

- MSP-FET430 (95 pages)

- TMS320TCI6486 (160 pages)

- TPS2330 (22 pages)

- DM648 DSP (47 pages)

- TMS320DM36X (134 pages)

- MSC1211 (35 pages)

- SPRAA56 (29 pages)

- DAC7741EVM (28 pages)

- CDCM7005 (34 pages)

- TMS370 (99 pages)

- Adpater (37 pages)

- TMS320C6452 DSP (46 pages)