Texas Instruments MSP430x1xx User Manual

Page 43

Interrupt Processing

3-13

System Resets, Interrupts, and Operating Modes

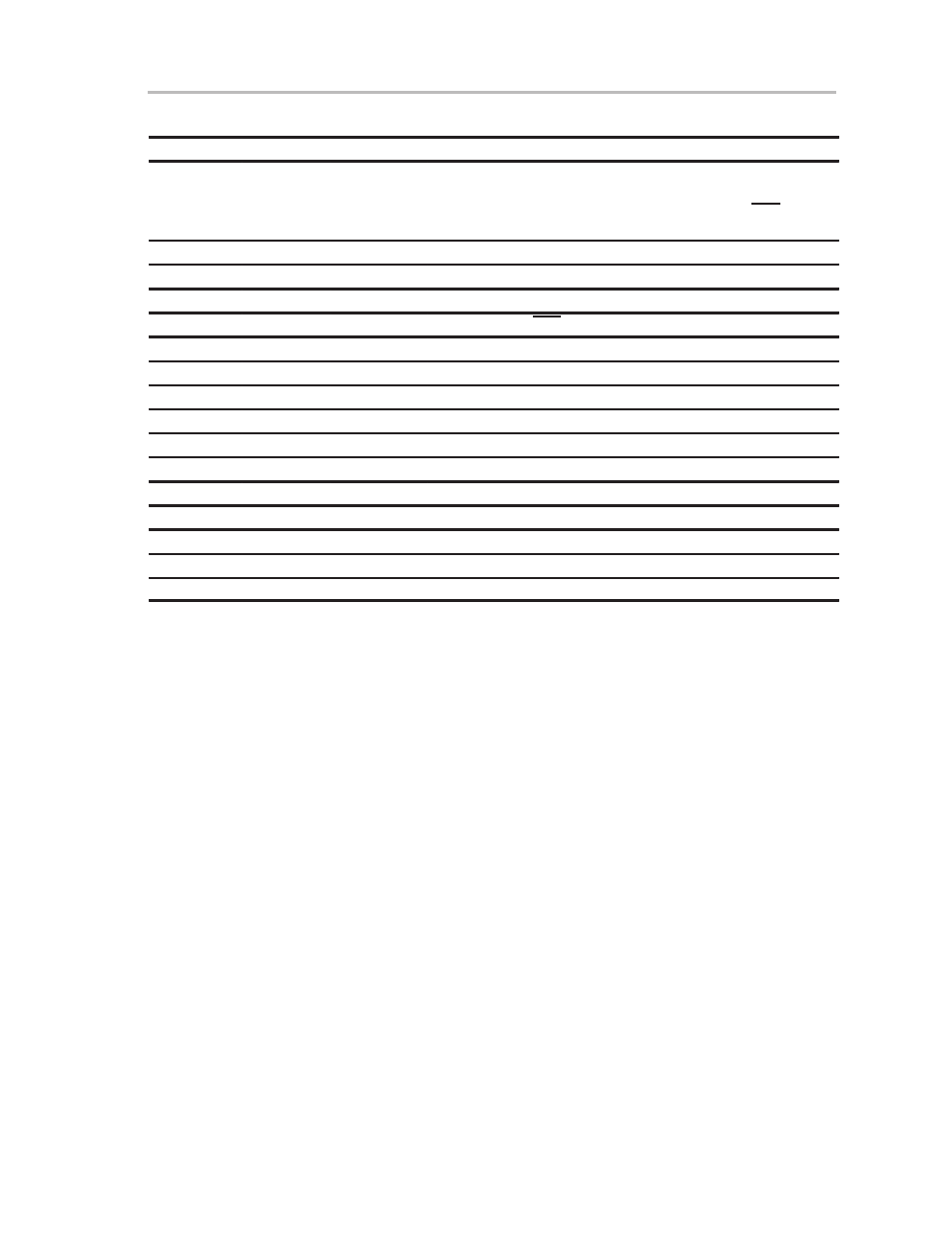

Table 3–3. Interrupt Flag Register 1 and 2

Bit Position

Short Form Initial State

Comments

IFG1.0

WDTIFG

Set

Set on watchdog timer overflow in watchdog mode or security key

violation.

Or reset

Reset with VCC power-up, or a reset condition at the RST/NMI pin

in reset mode.

IFG1.1

OFIFG

Set

Flag set on oscillator fault

IFG1.2

Not implemented

IFG1.3

Not implemented

IFG1.4

NMIIFG

Reset

Set through the RST/NMI pin

IFG1.5

Not implemented

IFG1.6

URXIFG0

Reset

USART0 receive flag (13x, 14x devices)

IFG1.7

UTXIFG0

Set

USART0 transmitter ready (13x, 14x devices)

IFG2.0

Not implemented

IFG2.1

Not implemented

IFG2.2

Not implemented

IFG2.3

Not implemented

IFG2.4

URXIFG1

Reset

USART1 receive flag (14x devices)

IFG2.5

UTXIFG1

Set

USART1 transmitter ready (14x devices)

IFG2.6

Not implemented

IFG2.7

Not implemented

Note:

The configuration of some MSP430 devices may differ slightly from those in above table. Refer to specific device data

sheets for individual configurations.