1 timer_a control register tactl, Figure 10–27. timer_a control register tactl, Table 10–4.mode control – Texas Instruments MSP430x1xx User Manual

Page 165

Timer_A Registers

10-25

Timer_A

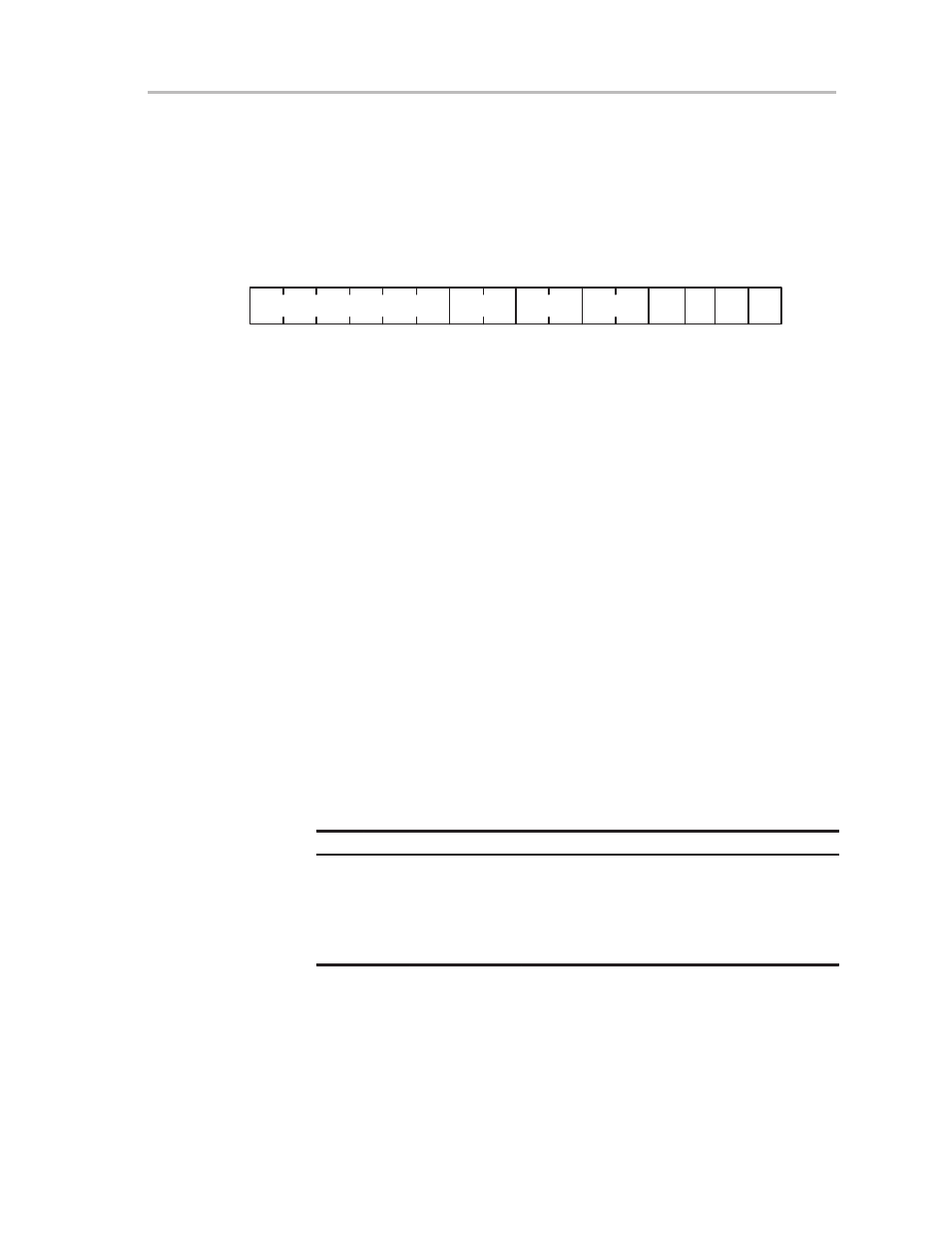

10.6.1 Timer_A Control Register TACTL

The timer and timer operation control bits are located in the timer control

register (TACTL) shown in Figure 10–27. All control bits are reset automati–

cally by the POR signal, but are not affected by the PUC signal. The control

register must be accessed using word instructions.

Figure 10–27. Timer_A Control Register TACTL

rw-

(0)

15

0

Unused

Input

Select

Input

Divider

Mode

Control

Un-

used

CLR TAIE TAIFG

TACTL

160h

rw-

(0)

rw-

(0)

rw-

(0)

rw-

(0)

rw-

(0)

rw-

(0)

rw-

(0)

rw-

(0)

rw-

(0)

rw-

(0)

rw

(0)

rw-

(0)

rw-

(0)

rw-

(0)

w-

(0)

Bit 0:

TAIFG: This flag indicates a timer overflow event.

Up mode:

TAIFG is set if the timer

counts from CCR0

value to 0000h.

Continuous mode:

TAIFG is set if the timer

counts from

0FFFFh to 0000h.

Up/down mode:

TAIFG is set if the timer

counts down from

0001h to 0000h.

Bit 1:

Timer overflow interrupt enable (TAIE) bit. An interrupt request from

the timer overflow bit is enabled if this bit is set, and is disabled if

reset.

Bit 2:

Timer clear (CLR) bit. The timer and input divider are reset with the

POR signal, or if bit CLR is set. The CLR bit is automatically reset

and is always read as zero. The timer starts in the upward direction

with the next valid clock edge, unless halted by cleared mode

control bits.

Bit 3:

Not used

Bits 4, 5: Mode control: Table 10–4 describes the mode control bits.

Table 10–4.Mode Control

MC1

MC0

Count Mode

Description

0

0

Stop

Timer is halted.

0

1

Up to CCR0

Timer counts up to CCR0 and restarts at 0.

1

0

Continuous up

Timer counts up to 0FFFFh and restarts at 0.

1

1

Up/down

Timer continuously

counts up to CCR0 and back

down to 0.

Bits 6, 7: Input divider control bits. Table 10–5 describes the input divider

control bits.