Texas Instruments MSP430x1xx User Manual

Page 428

Flash Memory Control Registers

C-16

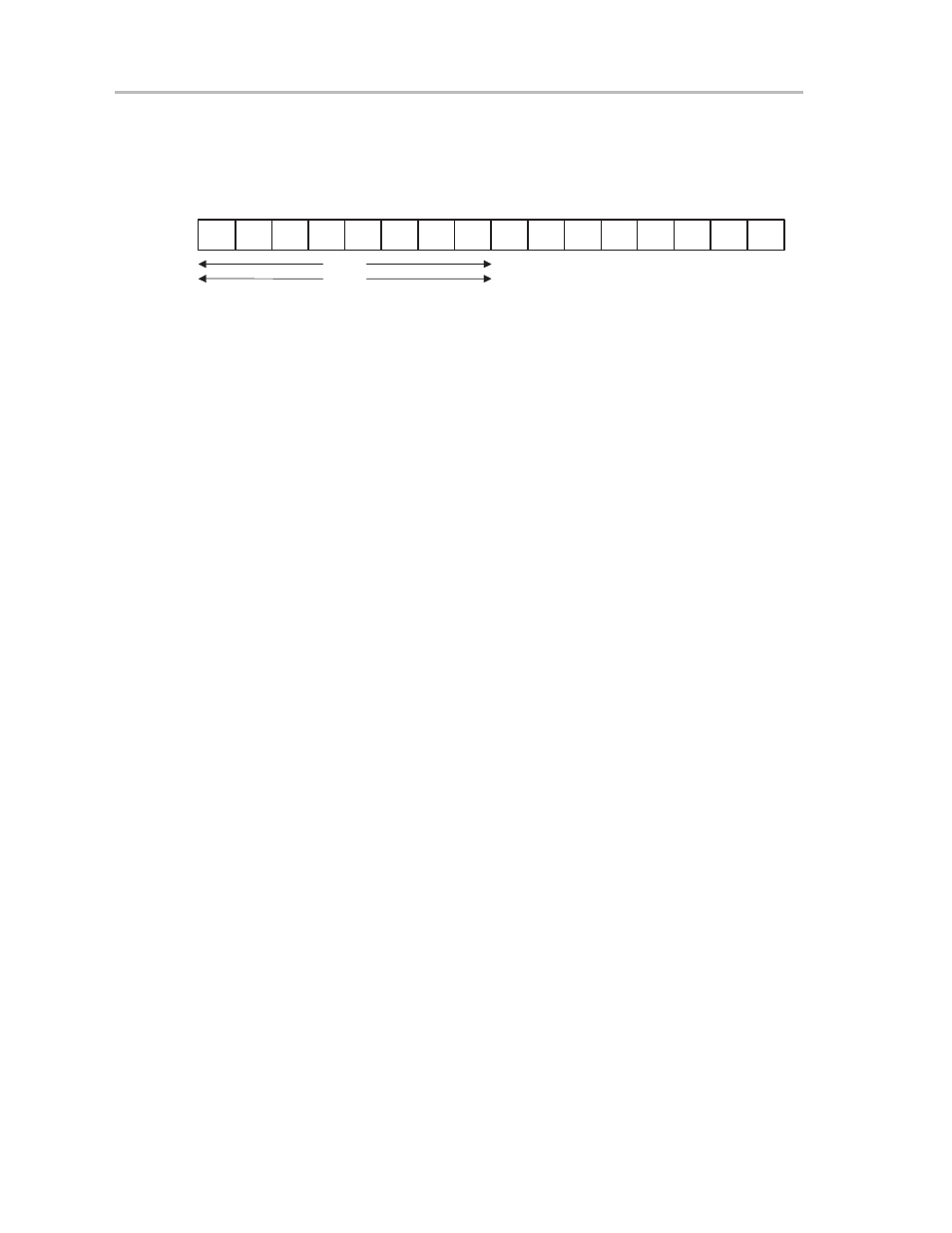

C.3.3 Flash Memory Control Register FCTL3

There are no restrictions on modifying this control register. The control bits are

reset or set (WAIT) by a PUC, but key violation bit KEYV is reset by POR.

7

0

KEYV

15

8

BUSY

Lock

ACCV

IFG

EMEX

res.

res.

FCTL3

012Ch

FCTL3 read:

FCTL3 write:

096h

0A5h

r0

r0

rw–0 rw–1 r–1

rw–0 rw–(0) r(w)–0

WAIT

BUSY

0128h, bit0,

The bit BUSY shows if an access to the flash memory is possible

(BUSY=0), or if an access violation can occur. The BUSY bit is read

only, but a write operation is allowed. The BUSY bit should be tested

before each write and erase cycle. The flash-timing generator

hardware immediately sets the BUSY bit after the start of a write

operation, a segment-write operation, a segment erase, or a mass-

erase. Once the timing generator has completed its function, the BUSY

bit is reset by hardware.

The program and erase timing are shown in Figures C–7, C–8, and

C–9.

0:

Flash memory is not busy. Read, write, erase and mass-erase are

possible without any violation of the internal flash timing. The

BUSY bit is reset by POR and by the flash timing generator.

1:

Flash memory is busy. Remains in busy state if segment write

function is in

wait mode.

The conditions for access to the flash memory during BUSY=1 are

described in paragraph C.2.6.

KEYV,

012Ch, bit1,

Key Violated.

0:

Key 0A5h (high byte) was not violated.

1:

Key 0A5h (high byte) was violated. Violation occurs when a write

access to register FCTL1, FCTL2 or FCTL3 is executed and the

high byte is not equal to 0A5h. If the security key is violated, bit

KEYV is set and a PUC is performed. The KEYV bit can be used

to determine the source that forced a start of the program at the

reset vector’s address. The KEYV bit is not automatically reset and

should reset by software.

Note: Any key violation results in a PUC, independent of the state of the

KEYV bit. To avoid endless software loops, the flash memory

control registers should not be written during a key violation

service routine.

Note: The software can set the KEYV bit. A PUC is also performed if

it is set by software.