Texas Instruments MSP430x1xx User Manual

Page 223

Asynchronous Operation

12-7

USART Peripheral Interface, UART Mode

12.3.3 Asynchronous Communication Formats

The USART module supports two multiprocessor communication formats

when asynchronous mode is used. These formats can transfer information

between many microcomputers on the same serial link. Information is

transferred as a block of frames from a particular source to one or more

destinations. The USART has features that identify the start of blocks and

suppress interrupts and status information from the receiver until a block start

is identified. In both multiprocessor formats, the sequence of data exchanged

with the USART module is based on data polling, or on the use of the receive

interrupt features.

Both of the asynchronous multiprocessor formats—idle-line and address-bit

—allow efficient data transfer between multiple communication systems. They

can also minimize the activity of the system to save current consumption or

processing resources.

The control register bit MM defines the address bit or idle-line multiprocessor

format. Both use the wake-up-on-transfer mode by activating the TXWake bit

(address feature function) and RXWake bit. The URXWIE and URXIE bits

control the transmit and receive features of these asynchronous

communication formats.

12.3.4 Idle-Line Multiprocessor Format

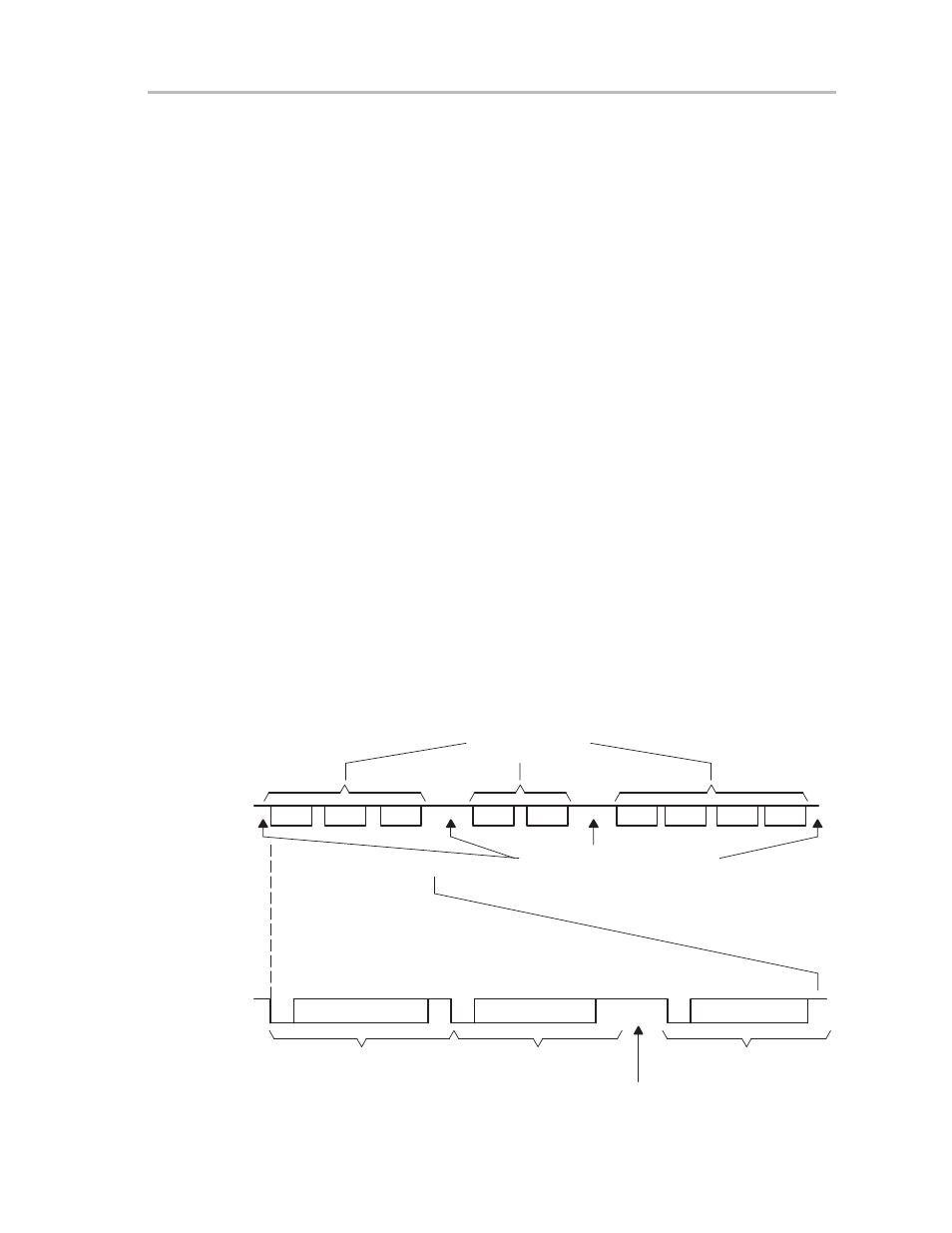

In the idle-line multiprocessor format, shown in Figure 12–7, blocks of data are

separated by an idle time. An idle-receive line is detected when ten or more

1s in a row are received after the first stop bit of a character.

Figure 12–7. Idle

-

Line Multiprocessor Format

ST

Address

SP ST

Data

SP

ST

Data

SP

Block of Frames

Idle Periods of 10 Bits or More

UTXD/URXD Expanded

UTXD/URXD

First Frame Within Block

is Address. It Follows Idle

Period of 10 Bits or More

Frame Within Block

Idle Period Less Than 10 Bits

Frame Within Block

UTXD/URXD