Texas Instruments MSP430x1xx User Manual

Page 68

CPU Registers

5-4

5.1.3

The Status Register (SR)

The status register SR contains the following CPU status bits:

-

V

Overflow bit

-

SCG1

System clock generator control bit 1

-

SCG0

System clock generator control bit 0

-

OscOff

Crystal oscillator off bit

-

CPUOff

CPU off bit

-

GIE

General interrupt enable bit

-

N

Negative bit

-

Z

Zero bit

-

C

Carry bit

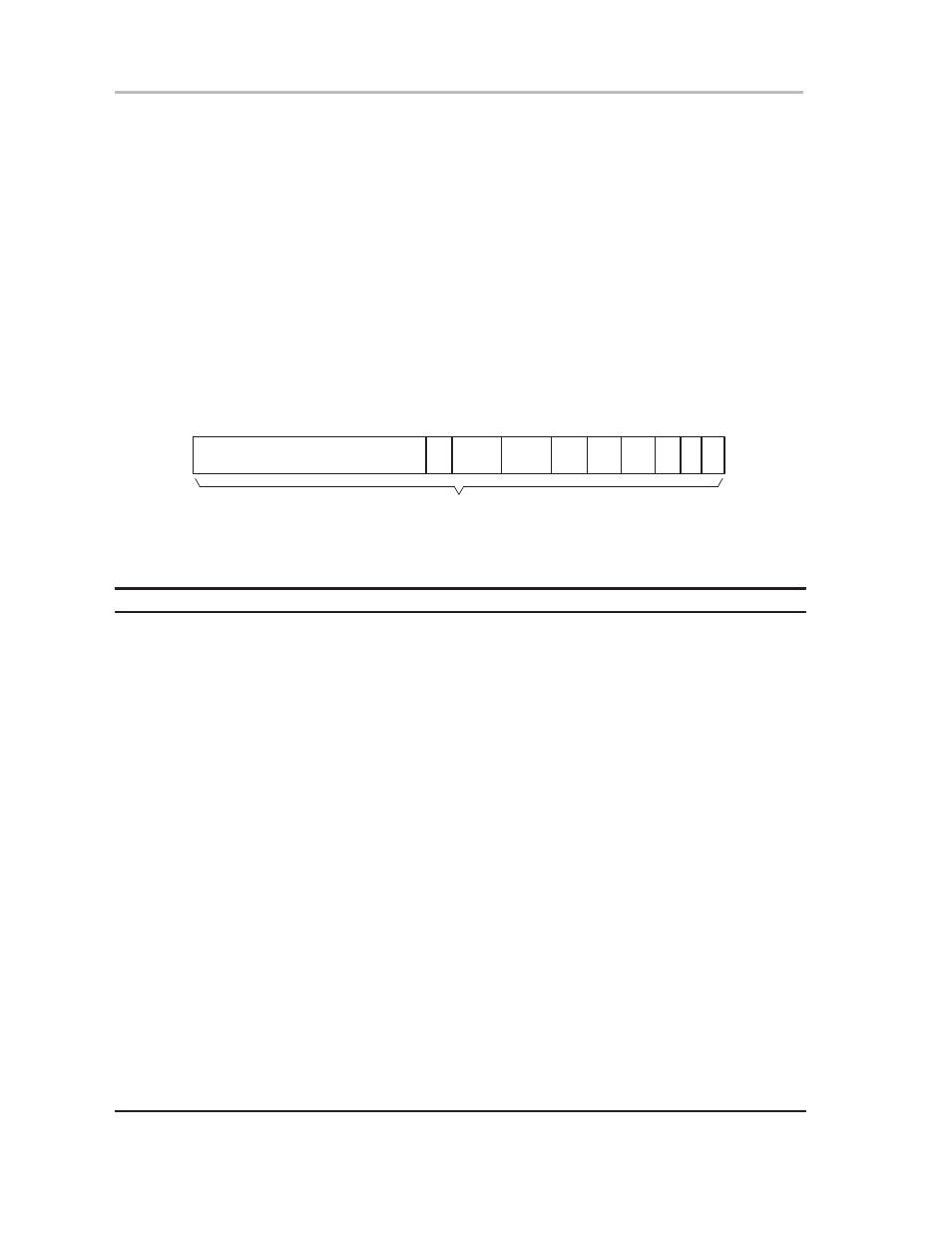

Figure 5–5 shows the SR bits.

Figure 5–5. Status Register Bits

SCG0

GIE

Z

C

rw-0

15

0

Reserved For Future Enhancements

N

CPU

Off

OSC

Off

SCG1

V

8

7

9

Table 5–2 describes the status register bits.

Table 5–2. Description of Status Register Bits

Bit

Description

V

Overflow bit. Set if the result of an arithmetic operation overflows the signed-variable range. The

bit is valid for both data formats, byte and word:

ADD(.B), ADDC(.B)

Set when:

Positive + Positive = Negative

Negative + Negative = Positive, otherwise reset

SUB(.B), SUBC(.B), CMP(.B)

Set when:

Positive – Negative = Negative

Negative – Positive = Positive, otherwise reset

SCG1, SCG0

These bits control four activity states of the system-clock generator and therefore influence the

operation of the processor system.

OscOFF

If set, the crystal oscillator enters off mode: all activities cease; however, the RAM contents, the

port, and the registers are maintained. Wake up is possible only through enabled external

interrupts when the GIE bit is set and from the NMI.

CPU Off

If set, the CPU enters off mode: program execution stops. However, the RAM, the port registers,

and especially the enabled peripherals (for example, Timer_A, UART, etc.) stay active. Wake

up is possible through all enabled interrupts.

GIE

If set, all enabled maskable interrupts are handled. If reset, all maskable interrupts are disabled.

The GIE bit is cleared by interrupts and restored by the RETI instruction as well as by other

appropriate instructions.

N

Set if the result of an operation is negative.

Word operation:

Negative bit is set to the value of bit 15 of the result

Byte operation:

Negative bit is set to the value of bit 7 of the result

Z

Set if the result of byte or word operation is 0; cleared if the result is not 0.

C

Set if the result of an operation produced a carry; cleared if no carry occurred. Some instructions

modify the carry bit using the inverted zero bits.