3 usart receive-interrupt operation, Figure 13–12. receive interrupt operation, Figure 13–13. receive interrupt state diagram – Texas Instruments MSP430x1xx User Manual

Page 259

Interrupt and Control Functions

13-13

USART Peripheral Interface, SPI Mode

13.4.3 USART Receive-Interrupt Operation

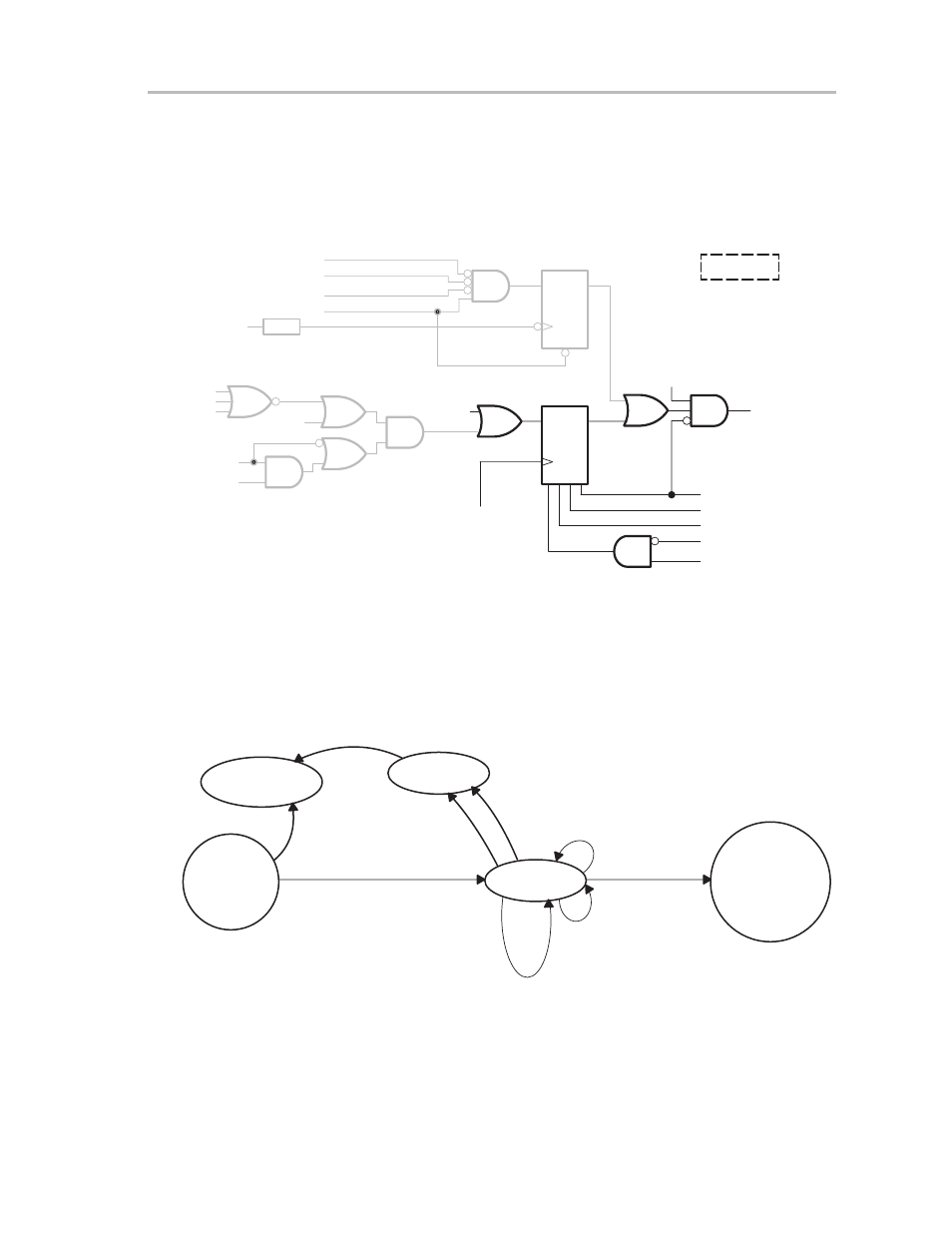

In the receive-interrupt operation shown in Figure 13–12, the receive-interrupt

flag URXIFG is set each time a character is received and loaded into the

receive buffer.

Figure 13–12. Receive Interrupt Operation

URXS

Clear

τ

(S)

SYNC

Valid Start Bit

Receiver Collects Character

URXSE

From URXD

SYNC

PE

FE

BRK

URXEIE

URXWIE

RXWake

Character Received

or

Master Overrun

URXIFG

URXIE

Request_

Interrupt_Service

SWRST

PUC

URXBUF Read

USPIE

IRQA

SYNC = 1

Clear

URXIFG is reset by a system reset PUC signal, or by a software reset

(SWRST). URXIFG is reset automatically if the interrupt is served or the

receive buffer URXBUF is read. The receive interrupt enable bit (USPIE), if set,

enables a CPU interrupt request as shown in Figure 13–13. The receive

interrupt flag bits URXIFG and USPIE are reset with a PUC signal or a SWRST.

Figure 13–13. Receive Interrupt State Diagram

Receive

Character

Completed

Interrupt

Service Started,

GIE = 0

URXIFG = 0

USPIE = 1

URXIFG = 1

USPIE = 1 and

GIE = 1 and

Priority Valid

GIE = 0

Priority

Too

Low

URXIFG = 0

Wait For Next

Start

USPIE = 0

SWRST = 1

PUC