Texas Instruments MSP430x1xx User Manual

Page 77

Addressing Modes

5-13

16-Bit CPU

5.2.6

Indirect Autoincrement Mode

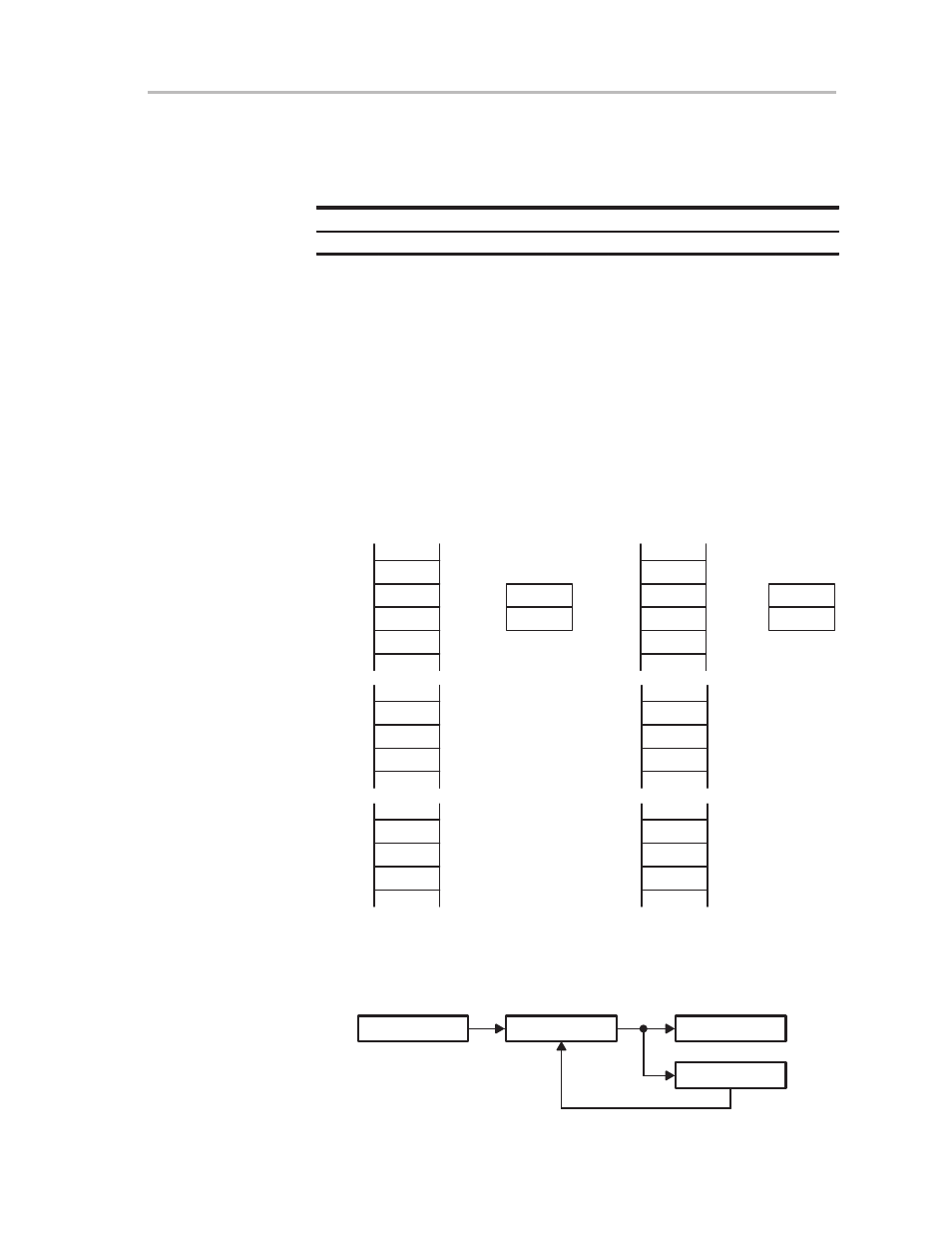

The indirect autoincrement mode is described in Table 5–10.

Table 5–10.Indirect Autoincrement Mode Description

Assembler Code

Content of ROM

MOV @R10+,0(R11)

MOV @R10+,0(R11)

Length:

One or two words

Operation:

Move the contents of the source address (contents of R10) to

the destination address (contents of R11). Register R10 is

incremented by 1 for a byte operation, or 2 for a word

operation after the fetch; it points to the next address without

any overhead. This is useful for table processing.

Comment:

Valid only for source operand. The substitute for destination

operand is 0(Rd) plus second instruction INCD Rd.

Example:

MOV @R10+,0(R11)

00000h

Address

Space

04ABBh

PC

0FF16h

0FF14h

0FF12h

0xxxxh

05BC1h

0FA34h

0FA32h

0FA30h

0xxxxh

0xxxxh

01234h

010AAh

010A8h

010A6h

0xxxxh

0FA32h

010A8h

R10

R11

Register

Before:

Address

Space

0xxxxh

05BC1h

0FA34h

0FA32h

0FA30h

0xxxxh

0xxxxh

05BC1h

010AAh

010A8h

010A6h

0xxxxh

0FA34h

R10

R11

Register

After:

0xxxxh

0xxxxh

0FF18h

00000h

04ABBh

PC

0FF16h

0FF14h

0FF12h

0xxxxh

0xxxxh

0FF18h

010A8h

The autoincrementing of the register contents occurs after the operand is

fetched. This is shown in Figure 5–6.

Figure 5–6. Operand Fetch Operation

Instruction

Address

Operand

+1/ +2