Texas Instruments MSP430x1xx User Manual

Page 33

System Reset and Initialization

3-3

System Resets, Interrupts, and Operating Modes

Note:

Generation of the POR/PUC signals does not necessarily generate a system

reset interrupt. Anytime a POR is activated, a system reset interrupt is

generated. However, when a PUC is activated, a system reset interrupt may

or may not be generated. Instead, a lower priority interrupt vector may be

generated, depending on what action caused the PUC. Each device data

sheet gives a detailed table of what action generates each interrupt. This

table should be consulted for the proper handling of all interrupts.

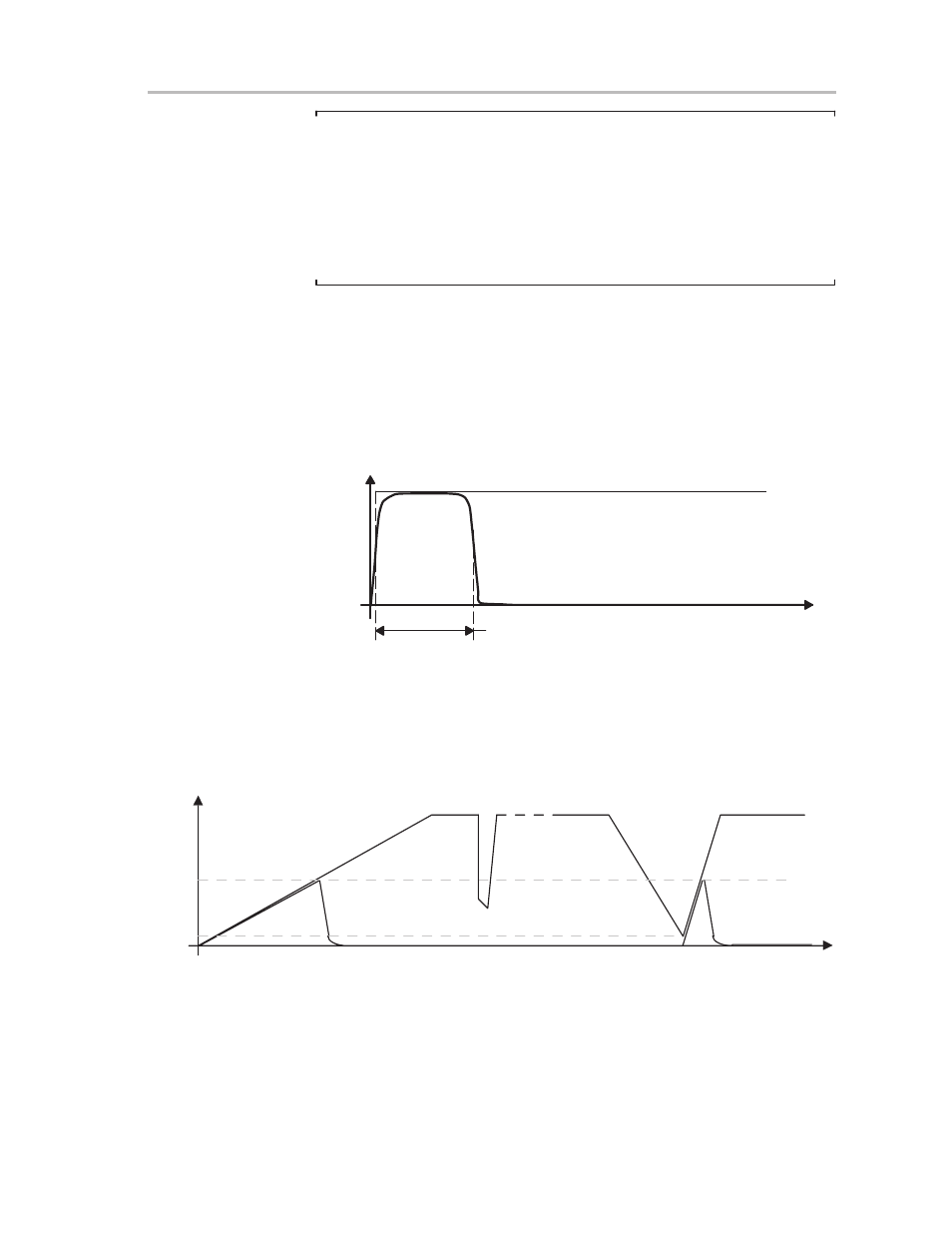

When the V

CC

supply provides a fast rise time as shown in Figure 3–2, the

POR delay provides enough active time on the POR signal to allow the signal

to initialize the circuitry correctly after power up. When the V

CC

rise time is

slow, as shown in Figure 3–3, the POR detector holds the POR signal active

until V

cc

has risen above the V

(POR)

level. This also ensures a correct

initialization.

Figure 3–2. Power-On Reset Timing on Fast V

CC

Rise Time

t

V

CC

POR

V

t

POR_Delay

If power to the chip is cycled, the supply voltage V

CC

must fall below the V

(min)

(see Figure 3–3) to ensure that another POR signal occurs when V

CC

is

powered up again. If V

CC

does not fall below V

(min)

during a cycle or a glitch,

a POR is not generated and power-up conditions do not set correctly.

Figure 3–3. Power-on Reset Timing on Slow V

CC

Rise Time

VCC

POR

V

t

V

(POR)

V

(min)

POR

No POR