Texas Instruments MSP430x1xx User Manual

Page 67

CPU Registers

5-3

16-Bit CPU

5.1.2.1

Examples for System SP Addressing (Refer to Figure 5–4)

MOV

SP,R4

; SP –> R4

MOV

@SP,R5

; Item I3 (TOS) –> R5

MOV

2(SP),R6

; Item I2 –> R6

MOV

R7,0(SP)

; Overwrite TOS with R7

MOV

R8,4(SP)

; Modify item I1

PUSH

R12

; Store R12 in address 0xxxh – 6; SP points to same address

POP

R12

; Restore R12 from address 0xxxh – 6; SP points to

0xxxh – 4

MOV

@SP+,R5

; Item I3 –> R5 (popped from stack); same as POP

instruction

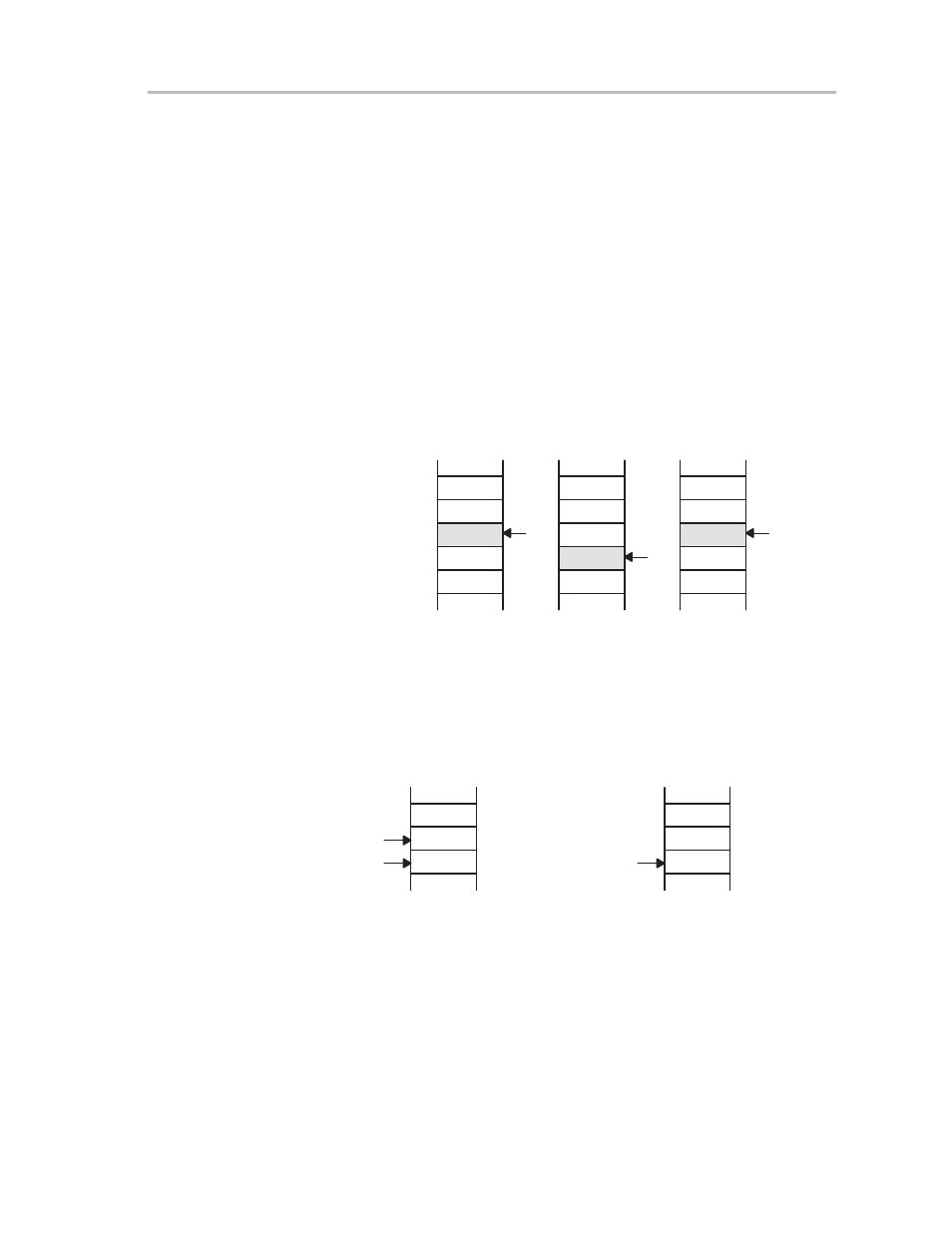

Figure 5–3 shows stack usage.

Figure 5–3. Stack Usage

I3

I1

I2

I3

0xxxh

0xxxh – 2

0xxxh – 4

0xxxh – 6

0xxxh – 8

I1

I2

SP

#1

SP

I1

I2

I3

SP

PUSH #1

POP R8

Address

5.1.2.2

Special Cases—PUSH SP and POP SP

The special cases of using the SP as an argument to the PUSH and POP

instructions are described below.

Figure 5–4. PUSH SP and POP SP

SP

1

SP

old

SP

1

PUSH SP

The stack pointer is changed after

a PUSH SP instruction.

SP

1

SP

2

POP SP

The stack pointer is not changed

after a POP SP instruction.

After the sequence

PUSH SP

I

I

; SP1 is stack pointer after this instruction

POP SP

; SP2 is stack pointer after this instruction

The stack pointer is two bytes lower than before this sequence.