A.13 timer_a registers, word access (continued) – Texas Instruments MSP430x1xx User Manual

Page 346

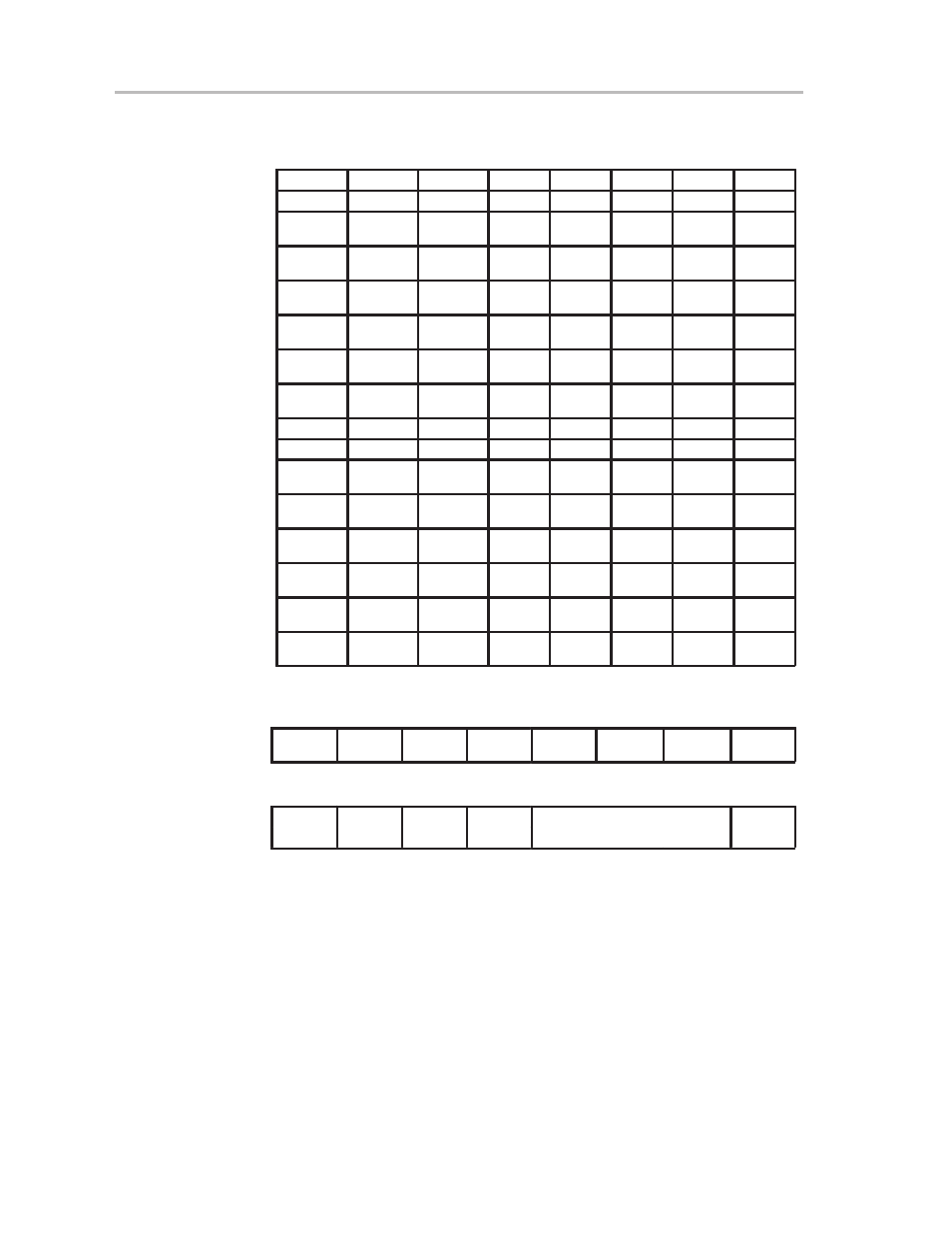

Timer_A Registers, Word Access (Continued)

A-14

A.13 Timer_A Registers, Word Access (Continued)

Bit # –

7

6

5

4

3

2

1

0

017Eh

017Ch

Cap/com register CCR4

†

017Ah

2

7

rw-(0)

2

6

rw-(0)

2

5

rw-(0)

2

4

rw-(0)

2

3

rw-(0)

2

2

rw-(0)

2

1

rw-(0)

2

0

rw-(0)

Cap/com register CCR3

†

0178h

2

7

rw-(0)

2

6

rw-(0)

2

5

rw-(0)

2

4

rw-(0)

2

3

rw-(0)

2

2

rw-(0)

2

1

rw-(0)

2

0

rw-(0)

Cap/com register CCR2

0176h

2

7

rw-(0)

2

6

rw-(0)

2

5

rw-(0)

2

4

rw-(0)

2

3

rw-(0)

2

2

rw-(0)

2

1

rw-(0)

2

0

rw-(0)

Cap/com register CCR1

0174h

2

7

rw-(0)

2

6

rw-(0)

2

5

rw-(0)

2

4

rw-(0)

2

3

rw-(0)

2

2

rw-(0)

2

1

rw-(0)

2

0

rw-(0)

Cap/com register CCR0

0172h

2

7

rw-(0)

2

6

rw-(0)

2

5

rw-(0)

2

4

rw-(0)

2

3

rw-(0)

2

2

rw-(0)

2

1

rw-(0)

2

0

rw-(0)

Timer_A register TAR

0170h

2

7

rw-(0)

2

6

rw-(0)

2

5

rw-(0)

2

4

rw-(0)

2

3

rw-(0)

2

2

rw-(0)

2

1

rw-(0)

2

0

rw-(0)

016Eh

016Ch

Cap/com control CCTL4

†

,

016Ah

OutMod42

rw-(0)

OutMod41

rw-(0)

OutMod40

rw-(0)

CCIE4

rw-(0)

CCI4

r

OUT4

rw-(0)

COV4

rw-(0)

CCIFG4

rw-(0)

Cap/com control CCTL3

†

,

0168h

OutMod32

rw-(0)

OutMod31

rw-(0)

OutMod30

rw-(0)

CCIE3

rw-(0)

CCI3

r

OUT3

rw-(0)

COV3

rw-(0)

CCIFG3

rw-(0)

Cap/com control CCTL2,

0166h

OutMod22

rw-(0)

OutMod21

rw-(0)

OutMod20

rw-(0)

CCIE2

rw-(0)

CCI2

r

OUT2

rw-(0)

COV2

rw-(0)

CCIFG2

rw-(0)

Cap/com control CCTL1,

0164h

OutMod12

rw-(0)

OutMod11

rw-(0)

OutMod10

rw-(0)

CCIE1

rw-(0)

CCI1

r

OUT1

rw-(0)

COV1

rw-(0)

CCIFG1

rw-(0)

Cap/com control CCTL0,

0162h

OutMod02

rw-(0)

OutMod01

rw-(0)

OutMod00

rw-(0)

CCIE0

rw-(0)

CCI0

r

OUT0

rw-(0)

COV0

rw-(0)

CCIFG0

rw-(0)

Timer_A control TACTL

0160h

ID1

rw-(0)

ID0

rw-(0)

MC1

rw-(0)

MC0

rw-(0)

Unused

rw-(0)

CLR

rw-(0)

TAIE

rw-(0)

TAIFG

rw-(0)

† Registers are reserved on devices with Timer_A3.

Bit # –

15

14

13

12

11

10

9

8

Timer_A interrupt vector

TAIV 12Eh

0

r0

0

r0

0

r0

0

r0

0

r0

0

r0

0

r0

0

r0

Bit # –

7

6

5

4

3

2

1

0

Timer_A interrupt vector

0

0

0

0

TAIV

0

Timer_A interru t vector

TAIV 12Eh

0

r0

0

r0

0

r0

0

r0

r-(0)

r-(0)

r-(0)

0

r0

TAIV Vector, Timer_A5 (five capture/compare blocks integrated)

0:

2:

4:

6:

8:

10:

No interrupt pending

CCIFG1 flag set, interrupt flag of capture/compare block 1

CCIFG2 flag set, interrupt flag of capture/compare block 2 (CCIFG1=0)

CCIFG3 flag set, interrupt flag of capture/compare block 3 (CCIFG1=CCIFG2=0)

CCIFG3 flag set, interrupt flag of capture/compare block 3 (CCIFG1=CCIFG2=CCIFG3=0)

TAIFG flag set, interrupt flag of Timer_A register/counter (CCIFG1=CCIFG2=CCIFG3=CCIFG4=0)

TAIV Vector, Timer_A3 (three capture/compare blocks integrated)

0:

2:

4:

6:

8:

10:

No interrupt pending

CCIFG1 flag set, interrupt flag of capture/compare block 1

CCIFG2 flag set, interrupt flag of capture/compare block 2 (CCIFG1=0)

Reserved

Reserved

TAIFG flag set, interrupt flag of Timer_A register/counter (CCIFG1=CCIFG2=CCIFG3=CCIFG4=0)