A.3 digital i/o, byte access – Texas Instruments MSP430x1xx User Manual

Page 335

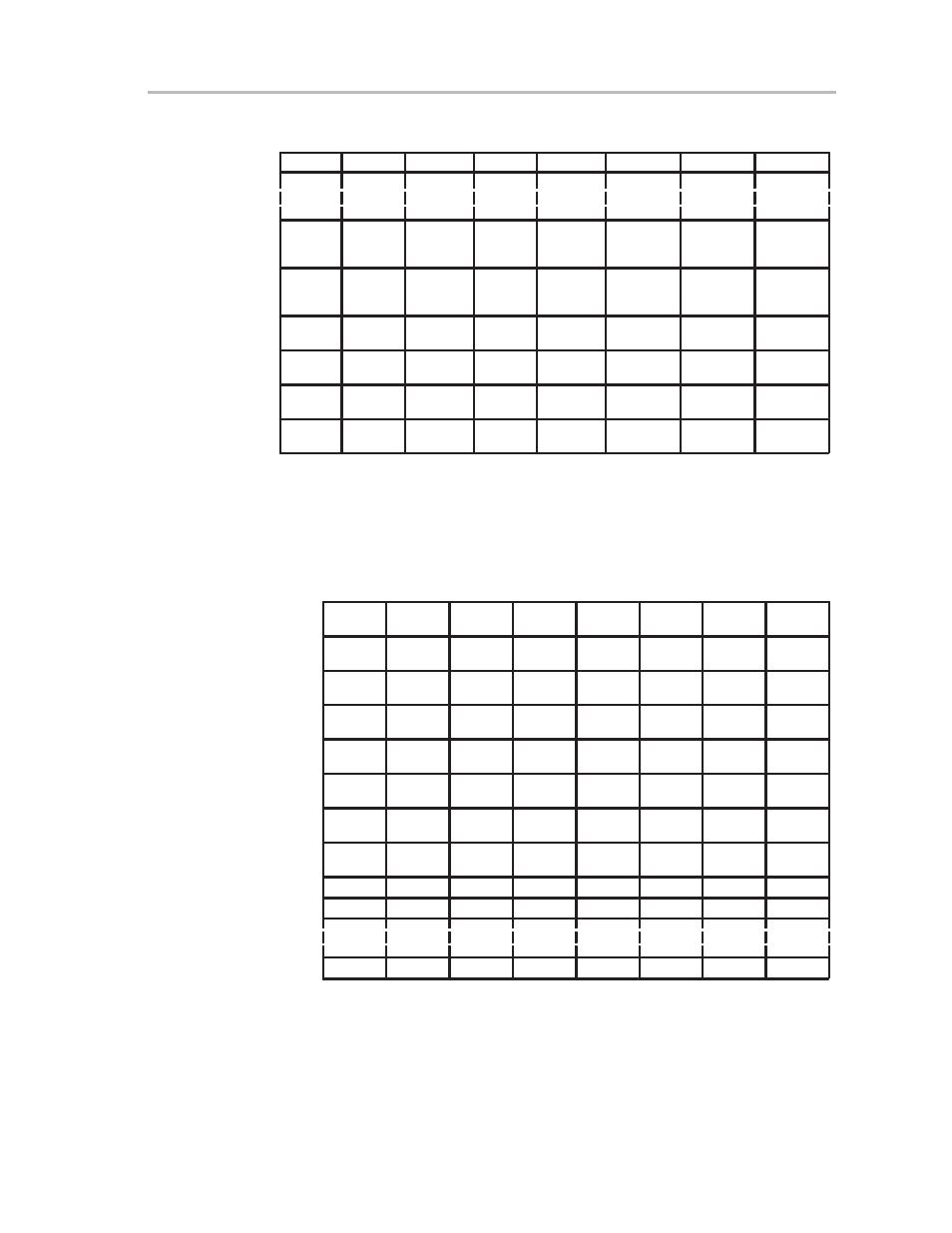

Special Function Register of MSP430x1xx Family, Byte Access

A-3

Peripheral File Map

A.2 Special Function Register of MSP430x1xx Family, Byte Access

000Fh

Module enable 2, ME2

0005h

UTXE1

rw-0

URXE1

USPIE1

rw-0

Module enable 1, ME1

0004h

UTXE0

rw-0

URXE0

USPIE0

rw-0

Interrupt flag 2, IFG2

0003h

UTXIFG1

rw-1

URXIFG1

rw-0

Interrupt flag 1, IFG1

0002h

UXIFG0

rw-1

URXIFG0

rw-0

NMIIFG

rw-0

OFIFG

rw-1

WDTIFG

rw-0

Interrupt enable 2, IE2

0001h

UTXIE1

rw-0

URXIE1

rw-0

Interrupt enable 1, IE1

0000h

UTXIE0

rw-0

URXIE0

rw-0

ACCVIE

rw-0

NMIIE

rw-0

OFIE

rw-0

WDTIE

rw-0

Note:

SFR bits are not implemented on devices without the corresponding peripheral.

A.3 Digital I/O, Byte Access

Bit # -

7

6

5

4

3

2

1

0

Function select, P4SEL

001Fh

P4SEL.7

rw-0

P4SEL.6

rw-0

P4SEL.5

rw-0

P4SEL.4

rw-0

P4SEL.3

rw-0

P4SEL.2

rw-0

P4SEL.1

rw-0

P4SEL.0

rw-0

Direction register, P4DIR

001Eh

P4DIR.7

rw-0

P4DIR.6

rw-0

P4DIR.5

rw-0

P4DIR.4

rw-0

P4DIR.3

rw-0

P4DIR.2

rw-0

P4DIR.1

rw-0

P4DIR.0

rw-0

Output register, P4OUT

001Dh

P4OUT.7

rw

P4OUT.6

rw

P4OUT.5

rw

P4OUT.4

rw

P4OUT.3

rw

P4OUT.2

rw

P4OUT.1

rw

P4OUT.0

rw

Input register, P4IN

001Ch

P4IN.7

r

P4IN.6

r

P4IN.5

r

P4IN.4

r

P4IN.3

r

P4IN.2

r

P4IN.1

r

P4IN.0

r

Function select, P3SEL

001Bh

P3SEL.7

rw-0

P3SEL.6

rw-0

P3SEL.5

rw-0

P3SEL.4

rw-0

P3SEL.3

rw-0

P3SEL.2

rw-0

P3SEL.1

rw-0

P3SEL.0

rw-0

Direction register, P3DIR

001Ah

P3DIR.7

rw-0

P3DIR.6

rw-0

P3DIR.5

rw-0

P3DIR.4

rw-0

P3DIR.3

rw-0

P3DIR.2

rw-0

P3DIR.1

rw-0

P3DIR.0

rw-0

Output register, P3OUT

0019h

P3OUT.7

rw

P3OUT.6

rw

P3OUT.5

rw

P3OUT.4

rw

P3OUT.3

rw

P3OUT.2

rw

P3OUT.1

rw

P3OUT.0

rw

Input register, P3IN

0018h

P3IN.7

r

P3IN.6

r

P3IN.5

r

P3IN.4

r

P3IN.3

r

P3IN.2

r

P3IN.1

r

P3IN.0

r

0017h

0016h

0010h