Texas Instruments MSP430x1xx User Manual

Page 327

ADC12 Control Registers

15-37

ADC12

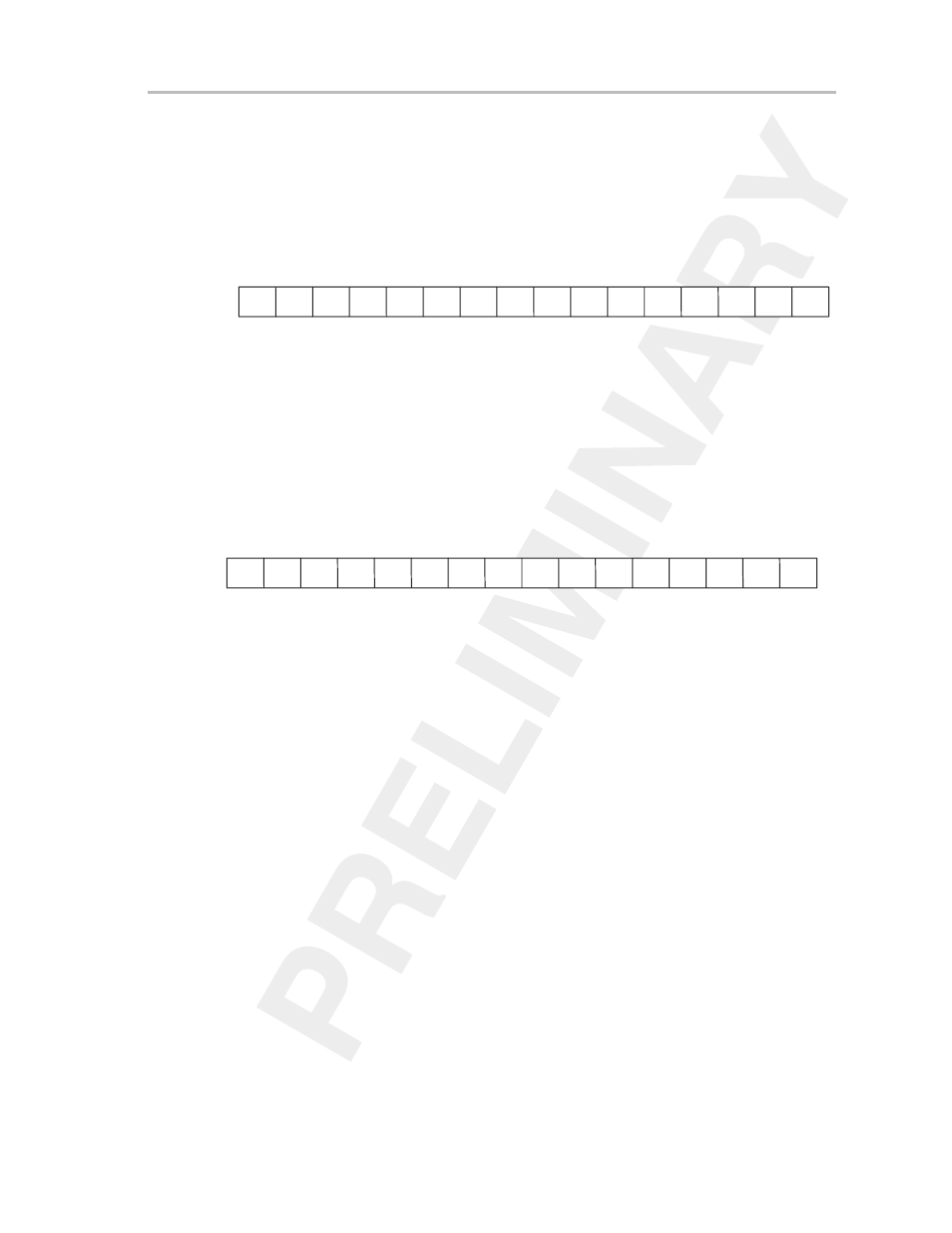

15.8.4 ADC12 Interrupt Flags ADC12IFG.x and Interrupt-Enable Registers

ADC12IEN.x

There are 16 ADC12IFG.x interrupt flags, 16 ADC12IE.x interrupt enable bits,

and one interrupt vector word. The interrupt flags and enable bits are

associated with the 16 ADC12MEMx registers.

All interrupt flags and interrupt-enable bits are reset during POR.

0

rw –(0)

rw –(0)

rw –(0) rw –(0)

0184h

ADC12IFG

15

rw –(0)

rw –(0)

rw –(0)

rw –(0)

rw –(0)

rw –(0)

rw –(0) rw –(0)

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

IFG.10

ADC

IFG.11

IFG.9

IFG.7

IFG.8

IFG.5

IFG.6

IFG.4

IFG.2

IFG.3

IFG.0

IFG.1

ADC

ADC

ADC

IFG.14

ADC

IFG.15

IFG.13

IFG.12

rw –(0)

rw –(0) rw –(0)

rw –(0)

ADC12IFG.x,

bits 0–15 The ADC12IFG.x interrupt flag is set if a conversion-result register

ADC12MEMx is loaded with the result of a conversion. The range for x

is 0 to 15.

The interrupt flags are reset if their corresponding ADC12MEMx

conversion-result register is accessed. To enable correct handling of

overflow conditions, they are not reset by accessing the interrupt vector

word ADC12IV. The overflow condition exists if another conversion result

is written to ADC12MEMx and the corresponding ADC12IFG.x is not

reset.

0

rw –(0)

rw –(0)

rw –(0) rw –(0)

rw –(0)

rw –(0)

01A6h

ADC12IE

15

ADC

rw –(0) rw –(0)

rw –(0)

rw –(0) rw –(0) rw –(0)

rw –(0)

rw –(0)

rw –(0)

rw –(0)

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

IE.10

ADC

IE.11

IE.9

IE.7

IE.8

IE.5

IE.6

IE.4

IE.2

IE.3

IE.0

IE.1

ADC

ADC

ADC

IE.14

ADC

IE.15

IE.13

IE.12

ADC12IE.x, bits 0–15

The ADC12IE.x interrupt-enable bit enables or disables the interrupt-

request service generated if the corresponding interrupt flag ADC12IFG.x

is set. The range for x is 0 to 15.

15.8.5 ADC12 Interrupt Vector Register ADC12IV

The 12-bit ADC has one interrupt vector to assist the handling of the 18

possible interrupt flags. Each of the 18 interrupt flags is prioritized and a unique

vector word is generated according to the highest-pending interrupt. The

priorities and corresponding vector-word values are shown in Table 15–3.

Overflow flag ADC12OVIFG has the highest priority, followed by timing-

overflow flag ADC12TOVIFG, and then by the interrupt flags for each

conversion-memory register ADC12IFG.0 to ADC12IFG.15.

The highest-pending interrupt flag generates a number from 0 (no interrupt is

pending) to 36. This encoded number can be added to the program counter

to automatically enter the software routine for handling each specific interrupt

(see software example, section 15.8.5.1.

An interrupt request is immediately generated if an interrupt flag is pending

(ADC12IV

≠

0), if the corresponding interrupt enable bit (ADC12OVIE,

ADC12TOVIE, or ADC12IE.x) is set, and if the general interrupt enable bit GIE

is set. When an interrupt request is generated, the service is requested by the

highest-priority interrupt that is enabled.