Figure 10–7. new period > old period, Figure 10–8. new period < old period – Texas Instruments MSP430x1xx User Manual

Page 148

Timer Modes

10-8

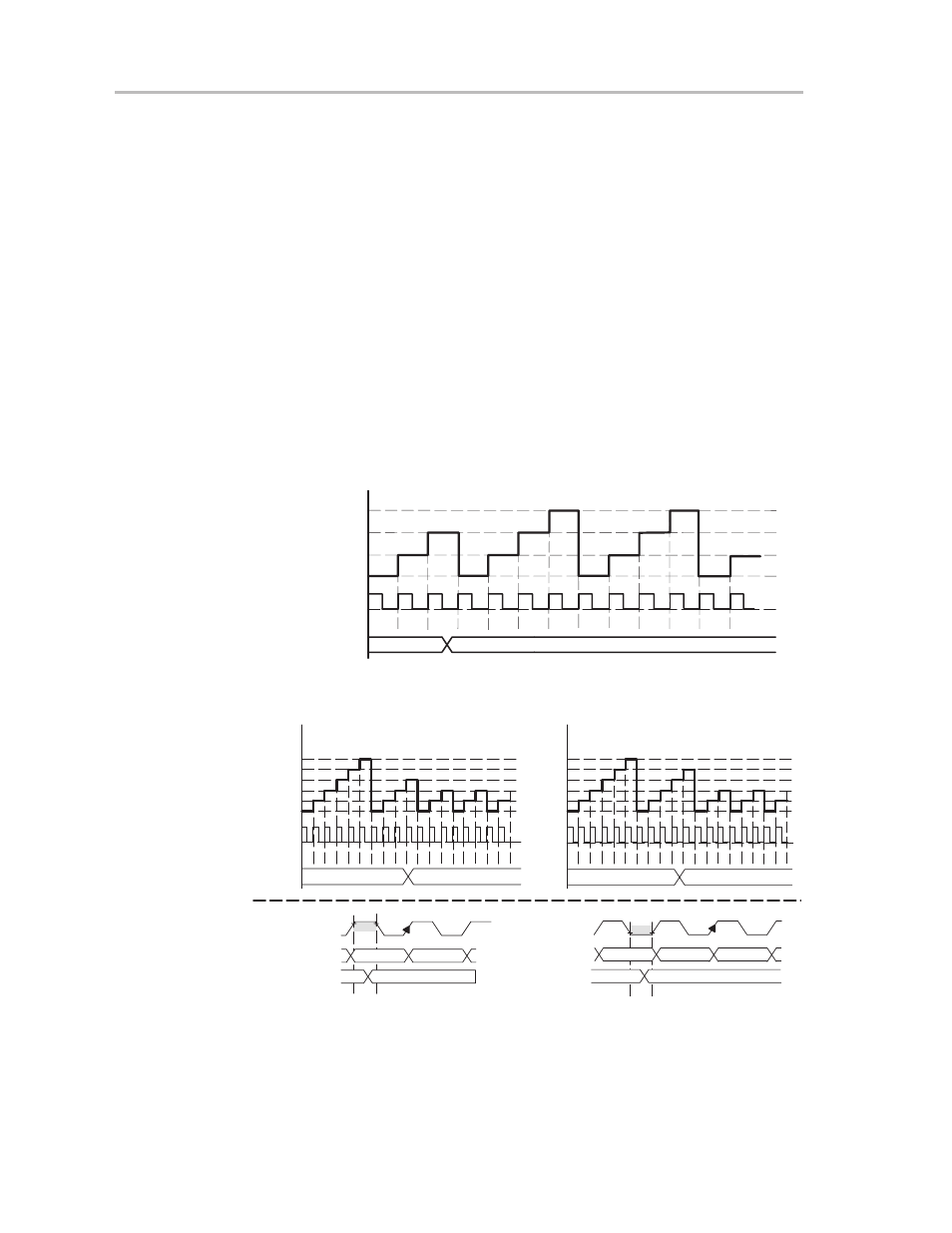

10.3.2.1 Timer in Up Mode—Changing the Period Register CCR0 Value

Changing the timer period register CCR0 while the timer is running can be a

little tricky. When the new period is greater than or equal to the old period, the

timer simply

counts up to the new period and no special attention is required

(see Figure 10–7). However, when the new period is less than the old period,

the phase of the timer clock during the CCR0 update affects how the timer

reacts to the new period.

If the new, smaller period is written to CCR0 during a high phase of the timer

clock, then the timer rolls to zero (or begins counting down when in the

up/down mode) on the next rising edge of the timer clock. However, if the new,

smaller period is written during a low phase of the timer clock, then the timer

continues to increment with the old period for one more clock cycle before

adopting the new period and rolling to zero (or beginning counting down). This

is shown in Figure 10–8.

Figure 10–7. New Period > Old Period

2

0

ППППП

ППППП

0

1

1

2

3

0

1

2

3

0

1

2

3

CCR0old = 2

CCR0new = 3

3

2

1

0

CCR0

Timer

Register

Figure 10–8. New Period < Old Period

CCR0old = 5

CCR0new = 2

Timer

Register

5

4

3

2

1

0

0 1 2 3 4 5 0 1 2 3 0 1 2 0 1 2 0 1

5

2

0 1 2 3 4 5 0 1 2 3 4 0 1 2 0 1 2 0 1

5

2

Timer

Register

5

4

3

2

1

0

CCR0old = 5

CCR0new = 2

CCR0

CCR0

CCR0 Loaded With 2 During High Clock Phase

CCR0 Loaded With 2 During Low Clock Phase

Timer Clock

Timer

CCR0

Timer Clock

Timer

CCR0

n

0 or n–1†

CCRold

CCRnew

CCRold

CCRnew

n

n+1

0 or n†

Load New CCR0

During High Phase of Clock

Load New CCR0

During Low Phase of Clock

† Up mode: 0; up/down mode: n–1

† Up mode: 0; up/down mode: n