Texas Instruments MSP430x1xx User Manual

Page 251

Synchronous Operation

13-5

USART Peripheral Interface, SPI Mode

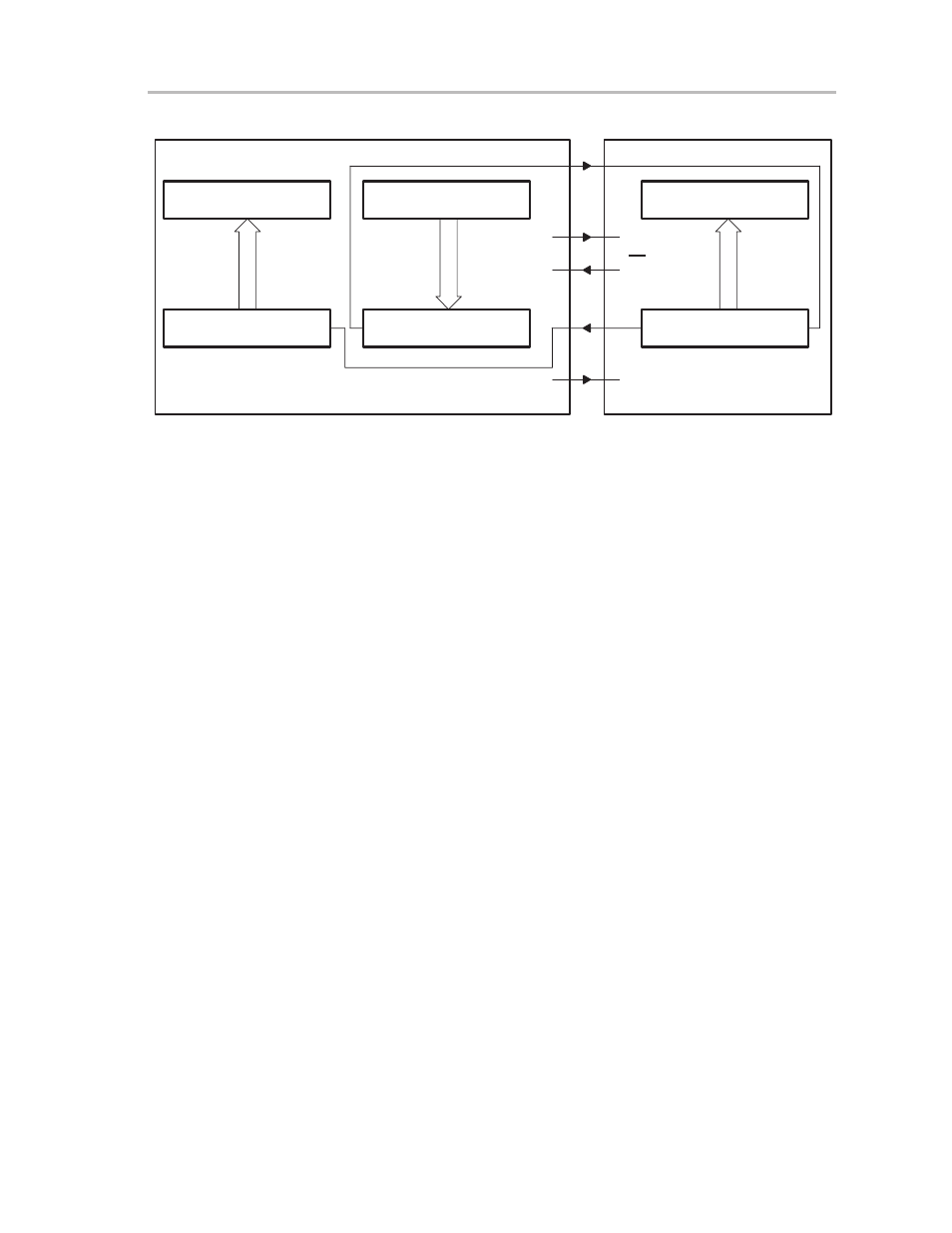

Figure 13–3. MSP430 USART as Master, External Device With SPI as Slave

Receive Buffer URXBUF

Receive Shift Register

MSB

LSB

Transmit Buffer UTXBUF

Transmit Shift Register

MSB

LSB

SPI Receive Buffer

Data Shift Register (DSR)

MSB

LSB

SOMI

SOMI

SIMO

SIMO

MASTER

SLAVE

Px.x

STE

STE

SS

Port.x

UCLK

SCLK

MSP430 USART

COMMON SPI

The master initiates the transfer by sending the UCLK signal. For the master,

data is shifted out of the transmit shift register on one clock edge, and shifted

into the receive shift register on the opposite edge. For the slave, the data

shifting operation is the same and uses one common register for transmitting

and receiving data. Master and slave send and receive data at the same time.

Whether the data is meaningful or dummy data depends on the application

software:

-

Master sends data and slave sends dummy data

-

Master sends data and slave sends data

-

Master sends dummy data and slave sends data

Figures 13–4 and 13–5 show an example of a serial synchronous data transfer

for a character length of seven bits. The initial content of the receive shift

register is 00. The following events occur in order:

A) Slave writes 98h to the data shift register (DSR) and waits for the master

to shift data out.

B) Master writes B0h to UTXBUF, which is immediately transferred to the

transmit shift register, and starts the transmission.

C) First character is finished and sets the interrupt flags.

D) Slave reads 58h from the receive buffer (right justified).

E) Slave writes 54h to the DSR and waits for the master to shift out data.

F) Master reads 4Ch from the receive buffer URXBUF (right justified).

G) Master writes E8h to the transmit buffer UTXBUF and starts the

transmission.

Note: If USART is in slave mode, no UCLK is needed after D), until G).

However, in master mode, two clocks are used internally (not on UCLK

signal) to end transmit/receive of first character and prepare the

transmit/receive of the next character.