14 udphs endpoint status register – Rainbow Electronics AT91CAP9S250A User Manual

Page 899

899

6264A–CAP–21-May-07

AT91CAP9S500A/AT91CAP9S250A

44.5.14

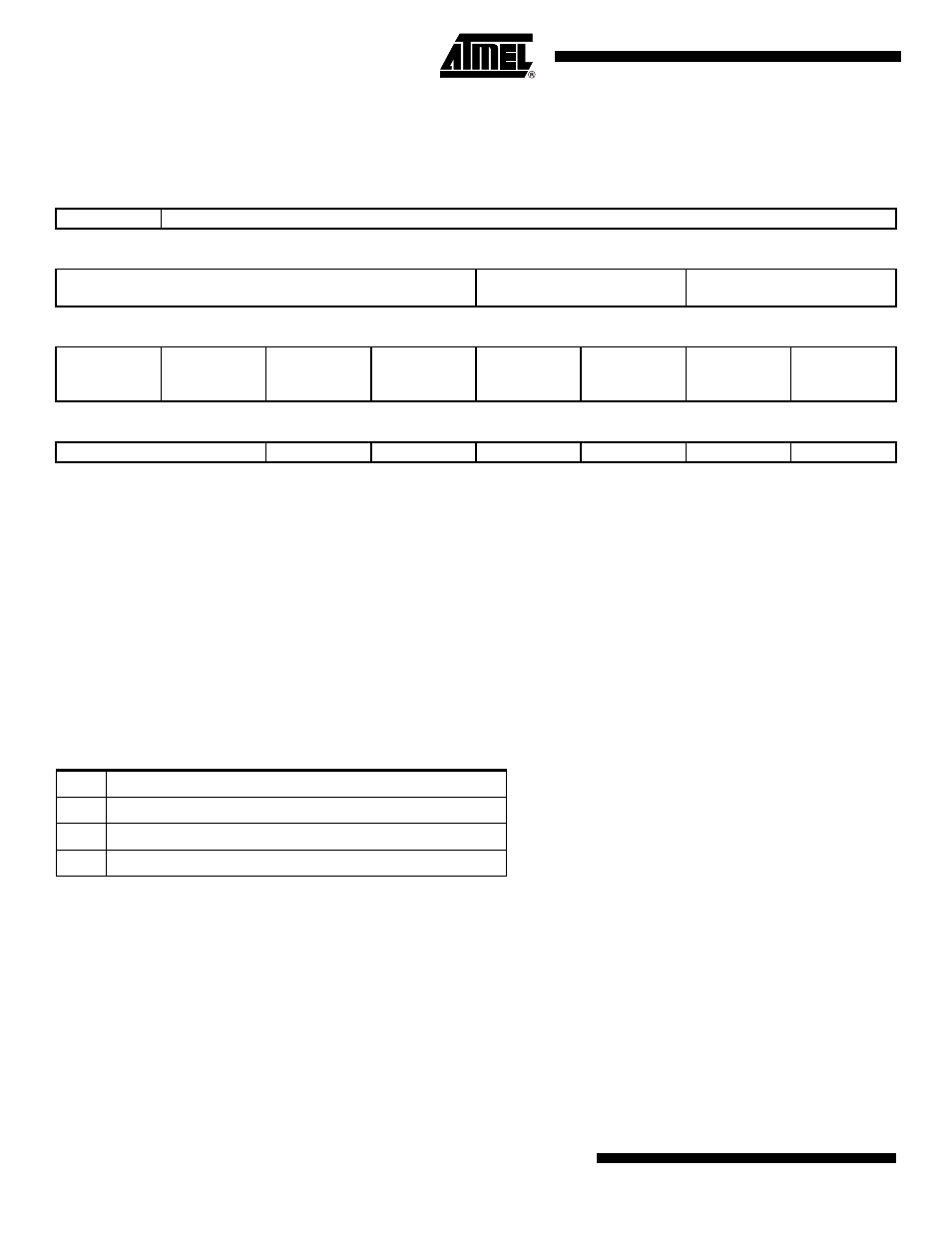

UDPHS Endpoint Status Register

Name:

UDPHS_EPTSTAx [x=0..7]

Access Type: Read-only

• FRCESTALL: Stall Handshake Request

0 = no effect.

1= If set a STALL answer will be done to the host for the next handshake.

This bit is reset by hardware upon received SETUP.

• TOGGLESQ_STA: Toggle Sequencing

Toggle Sequencing:

IN endpoint: it indicates the PID Data Toggle that will be used for the next packet sent. This is not relative to the current

bank.

CONTROL and OUT endpoint:

These bits are set by hardware to indicate the PID data of the current bank:

Note 1: In OUT transfer, the Toggle information is meaningful only when the current bank is busy (Received OUT

Data = 1).

Note 2:These bits are updated for OUT transfer:

– a new data has been written into the current bank.

– the user has just cleared the Received OUT Data bit to switch to the next bank.

Note 3: For High Bandwidth Isochronous Out endpoint, it is recommended to check the UDPHS_EPTSTAx/ERR_TRANS

bit to know if the toggle sequencing is correct or not.

Note 4: This field is reset to DATA1 by the UDPHS_EPTCLRSTAx register TOGGLESQ bit, and by UDPHS_EPTCTLDISx

(disable endpoint).

31

30

29

28

27

26

25

24

SHRT_PCKT

BYTE_COUNT

23

22

21

20

19

18

17

16

BYTE_COUNT

BUSY_BANK_STA

CURRENT_BANK/

CONTROL_DIR

15

14

13

12

11

10

9

8

NAK_OUT

NAK_IN/

ERR_FLUSH

STALL_SNT/

ERR_CRISO/

ERR_NBTRA

RX_SETUP/

ERR_FL_ISO

TX_PK_RDY/

ERR_TRANS

TX_COMPLT

RX_BK_RDY/

KILL_BANK

ERR_OVFLW

7

6

5

4

3

2

1

0

TOGGLESQ_STA

FRCESTALL

–

–

–

–

–

00

Data0

01

Data1

10

Data2 (only for High Bandwidth Isochronous Endpoint)

11

MData (only for High Bandwidth Isochronous Endpoint)