Rainbow Electronics AT91CAP9S250A User Manual

Page 748

748

6264A–CAP–21-May-07

AT91CAP9S500A/AT91CAP9S250A

40.5.3.4

Interrupts

Depending on the interrupt mask in the PWM_IMR register, an interrupt is generated at the

end of the corresponding channel period. The interrupt remains active until a read operation in

the PWM_ISR register occurs.

A channel interrupt is enabled by setting the corresponding bit in the PWM_IER register. A

channel interrupt is disabled by setting the corresponding bit in the PWM_IDR register.

40.6

Pulse Width Modulation (PWM) Controller User Interface

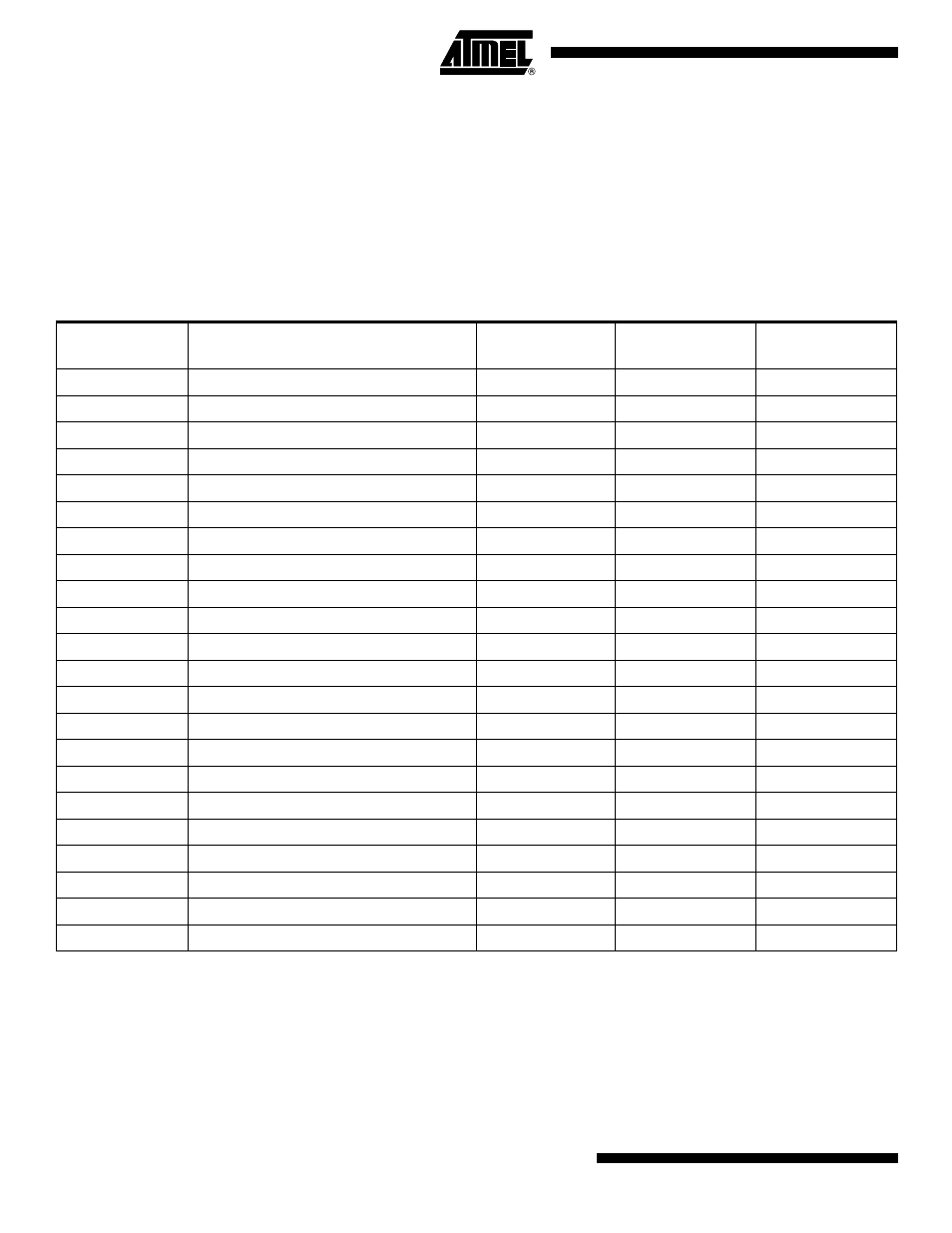

Table 40-2.

PWM Controller Registers

Offset

Register Name

Access

Peripheral

Reset Value

0x00

PWM Mode Register

PWM_MR

Read/Write

0

0x04

PWM Enable Register

PWM_ENA

Write-only

-

0x08

PWM Disable Register

PWM_DIS

Write-only

-

0x0C

PWM Status Register

PWM_SR

Read-only

0

0x10

PWM Interrupt Enable Register

PWM_IER

Write-only

-

0x14

PWM Interrupt Disable Register

PWM_IDR

Write-only

-

0x18

PWM Interrupt Mask Register

PWM_IMR

Read-only

0

0x1C

PWM Interrupt Status Register

PWM_ISR

Read-only

0

0x4C - 0xFC

Reserved

–

–

–

0x100 - 0x1FC

Reserved

0x200

Channel 0 Mode Register

PWM_CMR0

Read/Write

0x0

0x204

Channel 0 Duty Cycle Register

PWM_CDTY0

Read/Write

0x0

0x208

Channel 0 Period Register

PWM_CPRD0

Read/Write

0x0

0x20C

Channel 0 Counter Register

PWM_CCNT0

Read-only

0x0

0x210

Channel 0 Update Register

PWM_CUPD0

Write-only

-

...

Reserved

0x220

Channel 1 Mode Register

PWM_CMR1

Read/Write

0x0

0x224

Channel 1 Duty Cycle Register

PWM_CDTY1

Read/Write

0x0

0x228

Channel 1 Period Register

PWM_CPRD1

Read/Write

0x0

0x22C

Channel 1 Counter Register

PWM_CCNT1

Read-only

0x0

0x230

Channel 1 Update Register

PWM_CUPD1

Write-only

-

...

...

...

...

...