7 udphs test register, Udphs test register – Rainbow Electronics AT91CAP9S250A User Manual

Page 885

885

6264A–CAP–21-May-07

AT91CAP9S500A/AT91CAP9S250A

44.5.7

UDPHS Test Register

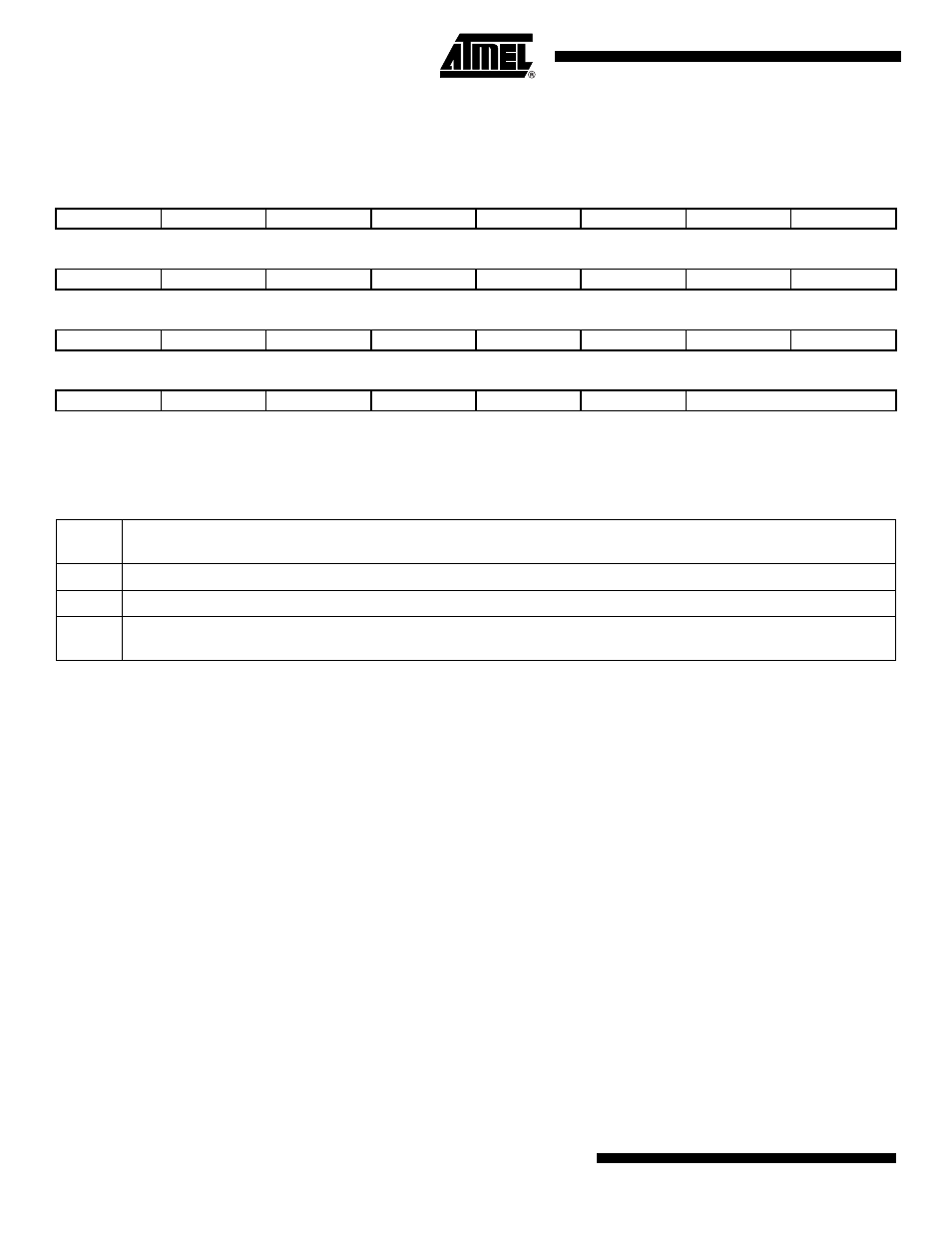

Name: UDPHS_TST

Access Type: Read/Write

• SPEED_CFG: Speed Configuration

Read/Write:

Speed Configuration:

• TST_J: Test J Mode

Read and write:

0 = no effect.

1 = set to send the J state on the UDPHS line. This enables the testing of the high output drive level on the D+ line.

• TST_K: Test K Mode

Read and write:

0 = no effect.

1 = set to send the K state on the UDPHS line. This enables the testing of the high output drive level on the D- line.

• TST_PKT: Test Packet Mode

Read and write:

0 = no effect.

1 = set to repetitively transmit the packet stored in the current bank. This enables the testing of rise and fall times, eye pat-

terns, jitter, and any other dynamic waveform specifications.

• OPMODE2: OpMode2

Read and write:

31

30

29

28

27

26

25

24

–

–

–

–

–

–

–

–

23

22

21

20

19

18

17

16

–

–

–

–

–

–

–

–

15

14

13

12

11

10

9

8

–

–

–

–

–

–

–

–

7

6

5

4

3

2

1

0

–

–

OPMODE2

TST_PKT

TST_K

TST_J

SPEED_CFG

00

Normal Mode: The macro is in Full Speed mode, ready to make a High Speed identification, if the host supports it and then

to automatically switch to High Speed mode

01

Reserved

10

Force High Speed: Set this value to force the hardware to work in High Speed mode. Only for debug or test purpose.

11

Force Full Speed: Set this value to force the hardware to work only in Full Speed mode. In this configuration, the macro will

not respond to a High Speed reset handshake