2 bcramc timing register – Rainbow Electronics AT91CAP9S250A User Manual

Page 260

260

6264A–CAP–21-May-07

AT91CAP9S500A/AT91CAP9S250A

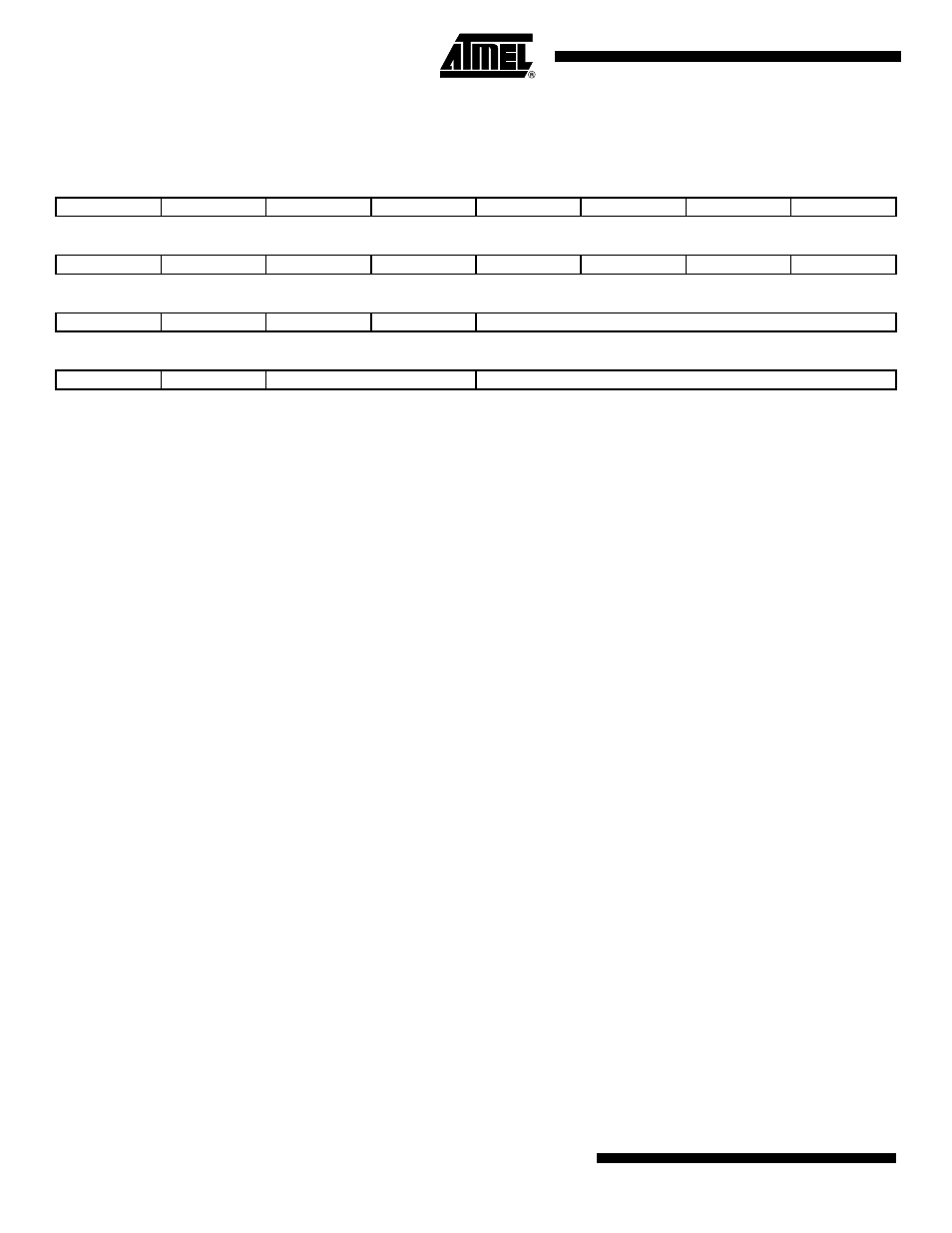

24.5.2

BCRAMC Timing Register

Register Name:

BCRAMC_TR

Access Type:

Read/Write

• TCW: Chip Enable to End of Write.

Reset value is 4.

This field defines the time between the falling edge of BCCS and the rising edge of BCWE in number of cycles. The Num-

ber of cycles is equal to TCW + 4. This time is used during initialization sequence since accesses to configuration registers

are done in asynchronous mode.

• TCRES: Control Register Enable Setup

Reset value is 0.

This field defines the time between the rising edge of cre and the falling edge of BCWE in number of cycles. The Number of

cycles is equal to TCRES + 1. This time is used during initialization sequence since accesses to configuration registers are

done in asynchronous mode.

• TCKA: BCWE High to BCCK Valid

Reset value is 0.

This field defines the time between the BCWE rising edge and BCCK switch on, in number of cycles. The number of cycles

is equal to TCKA + 2.5.

31

30

29

28

27

26

25

24

–

–

–

–

–

–

–

–

23

22

21

20

19

18

17

16

–

–

–

–

–

–

–

–

15

14

13

12

11

10

9

8

–

–

–

–

TCKA

7

6

5

4

3

2

1

0

–

–

TCRES

TCW