4 udphs interrupt status register, Section 44.5.4 ”udphs interrupt status register, Udph – Rainbow Electronics AT91CAP9S250A User Manual

Page 881: Udphs interrupt status register

881

6264A–CAP–21-May-07

AT91CAP9S500A/AT91CAP9S250A

44.5.4

UDPHS Interrupt Status Register

Name: UDPHS_INTSTA

Access Type: Read-only

• SPEED: Speed Status

0 = reset by hardware when the hardware is in Full Speed mode.

1 = set by hardware when the hardware is in High Speed mode

• DET_SUSPD: Suspend Interrupt

0 = cleared by setting the DET_SUSPD bit in UDPHS_CLRINT register

1 = set by hardware when a UDPHS Suspend (Idle bus for three frame periods, a J state for 3 ms) is detected. This triggers

a UDPHS interrupt when the DET_SUSPD bit is set in UDPHS_IEN register.

• MICRO_SOF: Micro Start Of Frame Interrupt

0 = cleared by setting the MICRO_SOF bit in UDPHS_CLRINT register.

1 = set by hardware when an UDPHS micro start of frame PID (SOF) has been detected (every 125 us) or synthesized by

the macro. This triggers a UDPHS interrupt when the MICRO_SOF bit is set in UDPHS_IEN. In case of detected SOF, the

MICRO_FRAME_NUM field in UDPHS_FNUM register

is incremented and the FRAME_NUMBER field doesn’t change.

Note:

The Micro Start Of Frame Interrupt (MICRO_SOF), and the Start Of Frame Interrupt (INT_SOF) are not generated at the same

time.

• INT_SOF: Start Of Frame Interrupt

0 = cleared by setting the INT_SOF bit in UDPHS_CLRINT.

1 = set by hardware when an UDPHS Start Of Frame PID (SOF) has been detected (every 1 ms) or synthesized by the

macro. This triggers a UDPHS interrupt when the INT_SOF bit is set in UDPHS_IEN register. In case of detected SOF, in

High Speed mode, the MICRO_FRAME_NUMBER field is cleared in UDPHS_FNUM register and the FRAME_NUMBER

field is updated.

• ENDRESET: End Of Reset Interrupt

0 = cleared by setting the ENDRESET bit in UDPHS_CLRINT.

1 = set by hardware when an End Of Reset has been detected by the UDPHS controller. This triggers a UDPHS interrupt

when the ENDRESET bit is set in UDPHS_IEN.

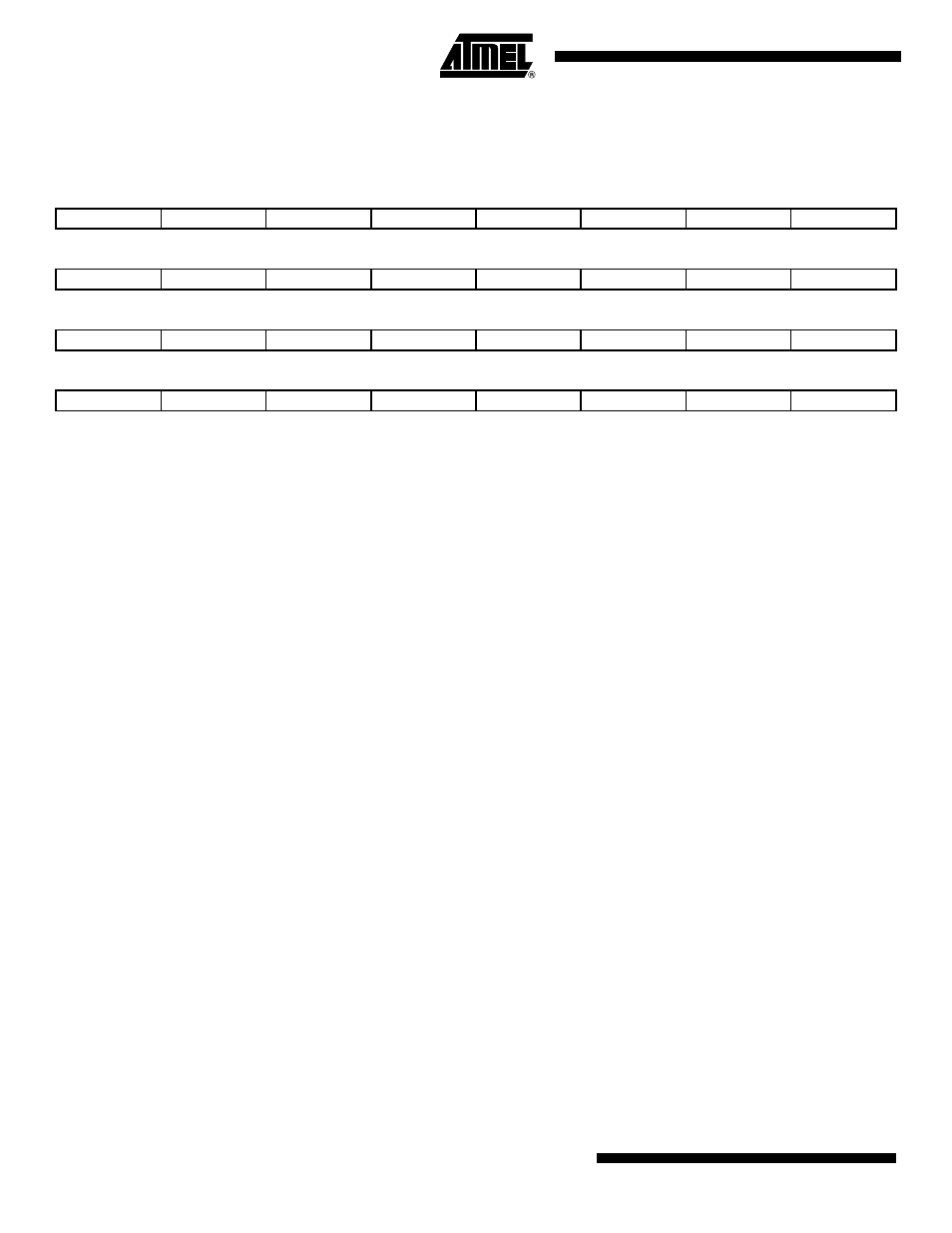

31

30

29

28

27

26

25

24

–

DMA_INT_6

DMA_INT_5

DMA_INT_4

DMA_INT_3

DMA_INT_2

DMA_INT_1

–

23

22

21

20

19

18

17

16

–

–

–

–

–

–

–

–

15

14

13

12

11

10

9

8

EPT_7

EPT_6

EPT_5

EPT_4

EPT_3

EPT_2

EPT_1

EPT_0

7

6

5

4

3

2

1

0

UPSTR_RES

ENDOFRSM

WAKE_UP

ENDRESET

INT_SOF

MICRO_SOF

DET_SUSPD

SPEED