6 timer counter (tc) user interface, Ed in – Rainbow Electronics AT91CAP9S250A User Manual

Page 663

663

6264A–CAP–21-May-07

AT91CAP9S500A/AT91CAP9S250A

38.6

Timer Counter (TC) User Interface

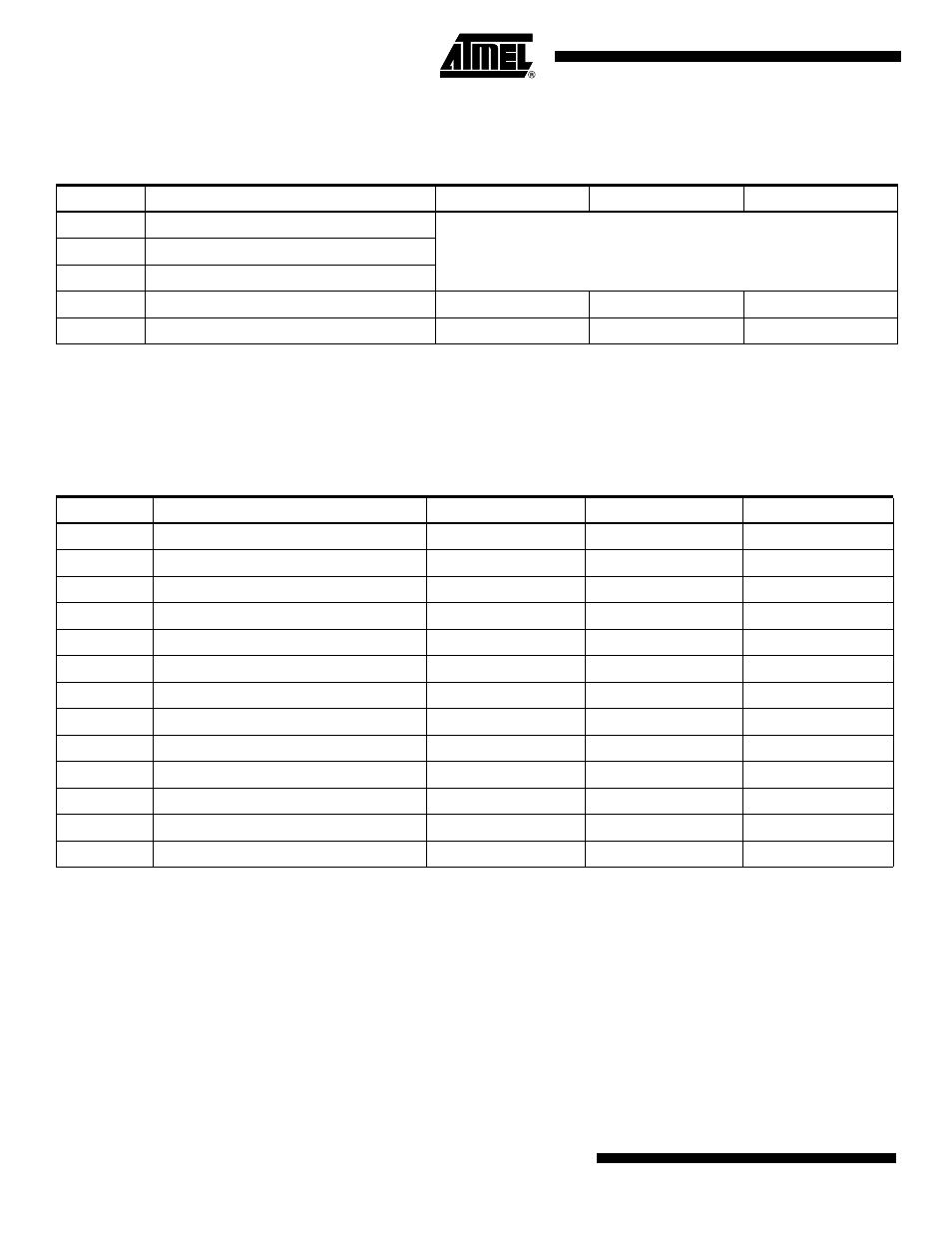

TC_BCR (Block Control Register) and TC_BMR (Block Mode Register) control the whole TC

block. TC channels are controlled by the registers listed in

. The offset of each of the

channel registers in

is in relation to the offset of the corresponding channel as men-

tioned in

Notes:

1. Read-only if WAVE = 0

Table 38-4.

TC Global Memory Map

Offset

Channel/Register

Name

Access

Reset Value

0x00

TC Channel 0

See

0x40

TC Channel 1

See

0x80

TC Channel 2

See

0xC0

TC Block Control Register

TC_BCR

Write-only

–

0xC4

TC Block Mode Register

TC_BMR

Read/Write

0

Table 38-5.

TC Channel Memory Map

Offset

Register

Name

Access Reset

Value

0x00

Channel Control Register

TC_CCR

Write-only

–

0x04

Channel Mode Register

TC_CMR

Read/Write

0

0x08

Reserved

–

0x0C

Reserved

–

0x10

Counter Value

TC_CV

Read-only

0

0x14

Register A

TC_RA

Read/Write

0

0x18

Register B

TC_RB

Read/Write

0

0x1C

Register C

TC_RC

Read/Write

0

0x20

Status Register

TC_SR

Read-only

0

0x24

Interrupt Enable Register

TC_IER

Write-only

–

0x28

Interrupt Disable Register

TC_IDR

Write-only

–

0x2C

Interrupt Mask Register

TC_IMR

Read-only

0

0xFC

Reserved

–

–

–