11 pmc clock generator pll b register – Rainbow Electronics AT91CAP9S250A User Manual

Page 375

375

6264A–CAP–21-May-07

AT91CAP9S500A/AT91CAP9S250A

29.9.11

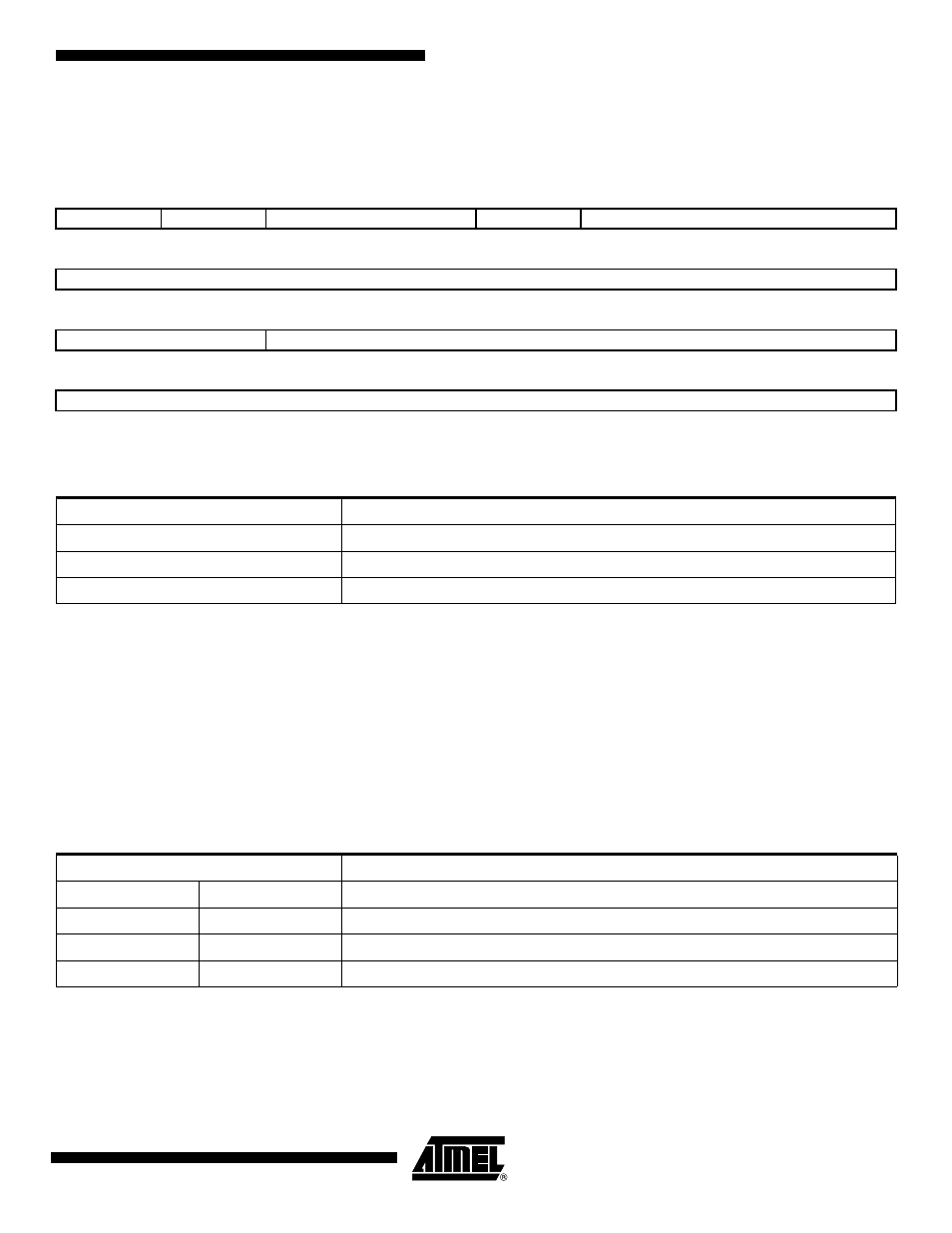

PMC Clock Generator PLL B Register

Register Name:

CKGR_PLLBR

Access Type:

Read/Write

Possible limitations on PLL B input frequencies and multiplier factors should be checked before using the PMC.

• DIVB: Divider B

• PLLBCOUNT: PLL B Counter

Specifies the number of slow clock cycles before the LOCKB bit is set in PMC_SR after CKGR_PLLBR is written.

• OUTB: PLLB Clock Frequency Range

To optimize clock performance, this field must be programmed as specified in “PLL Characteristics” in the Electrical Char-

acteristics section of the product datasheet.

• MULB: PLL B Multiplier

0 = The PLL B is deactivated.

1 up to 2047 = The PLL B Clock frequency is the PLL B input frequency multiplied by MULB + 1.

• USBDIV: Divider for USB Clock

31

30

29

28

27

26

25

24

–

–

USBDIV

–

MULB

23

22

21

20

19

18

17

16

MULB

15

14

13

12

11

10

9

8

OUTB

PLLBCOUNT

7

6

5

4

3

2

1

0

DIVB

DIVB

Divider Selected

0

Divider output is 0

1

Divider is bypassed

2 - 255

Divider output is the selected clock divided by DIVB.

USBDIV

Divider for USB Clock(s)

0

0

Divider output is PLL B clock output.

0

1

Divider output is PLL B clock output divided by 2.

1

0

Divider output is PLL B clock output divided by 4.

1

1

Reserved.