Rainbow Electronics AT91CAP9S250A User Manual

Page 303

303

6264A–CAP–21-May-07

AT91CAP9S500A/AT91CAP9S250A

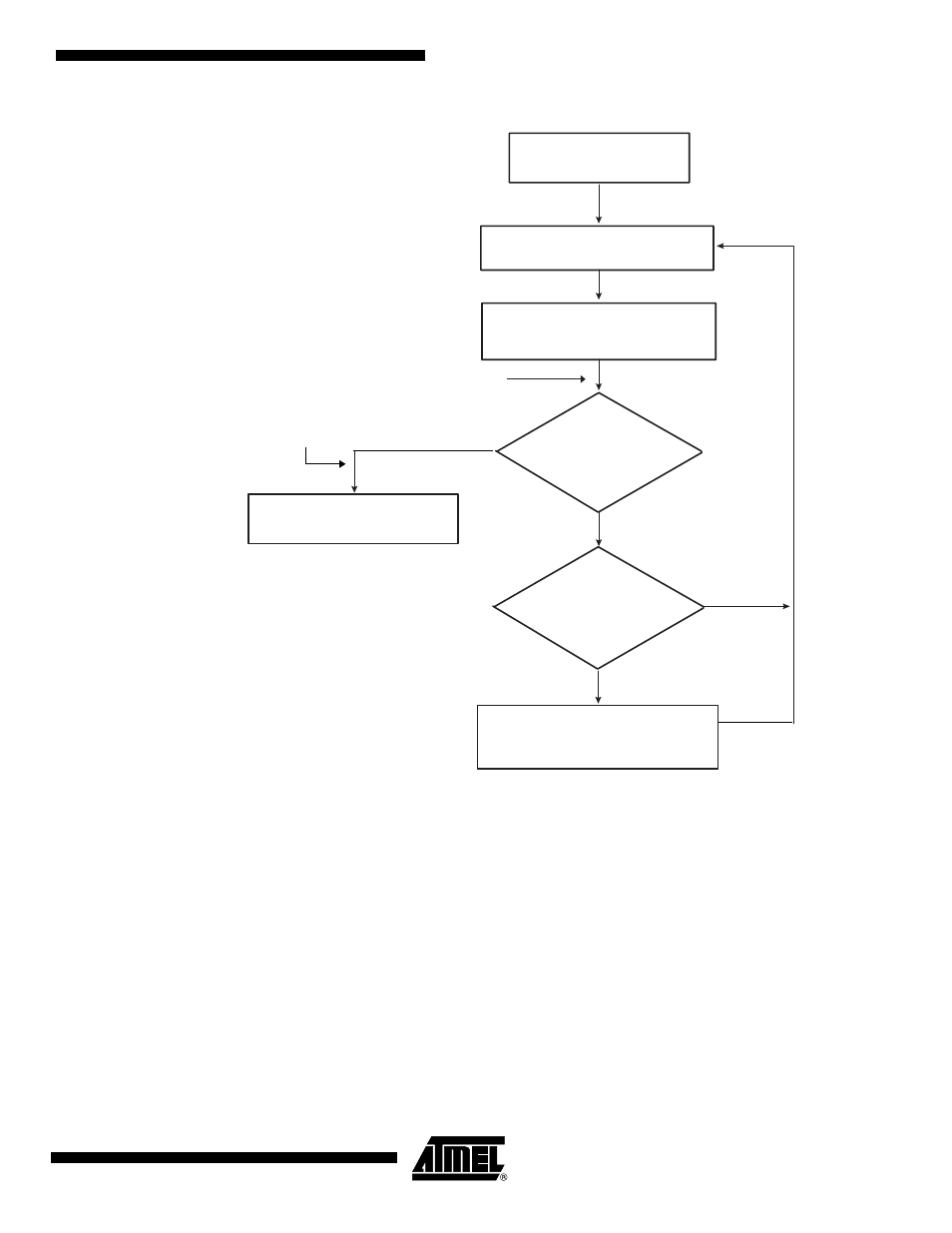

Figure 26-15. DMAC Transfer Replay Mode is Enabled for the Source and Contiguous Destination Address

26.3.5.7

Multi-buffer DMAC Transfer with Linked List for Source and Contiguous Destination Address (Row 2)

1.

Read the Channel Enable register to choose a free (disabled) channel.

2.

Set up the linked list in memory. Write the control information in the

LLI.DMAC_CTRLAx and LLI.DMAC_CTRLBx register location of the buffer descriptor

for each LLI in memory for channel x. For example, in the register, you can program the

following:

a.

Set up the transfer type (memory or non-memory peripheral for source and desti-

nation) and flow control device by programming the FC of the DMAC_CTRLBx

register.

b.

Set up the transfer characteristics, such as:

– i. Transfer width for the source in the SRC_WIDTH field.

– ii. Transfer width for the destination in the DST_WIDTH field.

– iii. Source AHB master interface layer in the SIF field where source resides.

– iv. Destination AHB master interface layer in the DIF field where destination resides.

Channel Enabled by

software

Buffer Transfer

Replay mode for SADDRx,

Contiguous mode for DADDRx

CTRLAx, CTRLBx

Channel Disabled by

hardware

Buffer Complete interrupt

generated here

Buffer Transfer Complete

interrupt generated here

yes

no

no

yes

Stall until STALLED field is

cleared by software writing

KEEPON Field

DMA_EBCIMR[x]=1?

Is HDMA in Row1of

HDMA State Machine Table?