3 processor clock controller, 4 usb clock controller – Rainbow Electronics AT91CAP9S250A User Manual

Page 355

355

6264A–CAP–21-May-07

AT91CAP9S500A/AT91CAP9S250A

Figure 29-1. Master Clock Controller

29.3

Processor Clock Controller

The PMC features a Processor Clock Controller (PCK) that implements the Processor Idle

Mode. The Processor Clock can be disabled by writing the System Clock Disable Register

(PMC_SCDR). The status of this clock (at least for debug purpose) can be read in the System

Clock Status Register (PMC_SCSR).

The Processor Clock PCK is enabled after a reset and is automatically re-enabled by any

enabled interrupt. The Processor Idle Mode is achieved by disabling the Processor Clock, which

is automatically re-enabled by any enabled fast or normal interrupt, or by the reset of the

product.

When the Processor Clock is disabled, the current instruction is finished before the clock is

stopped, but this does not prevent data transfers from other masters of the system bus.

29.4

USB Clock Controller

The USB Source Clock is always generated from the PLL B output. If using the USB, the user

must program the PLL to generate a 48 MHz, a 96 MHz or a 192 MHz signal with an accuracy of

± 0.25% depending on the USBDIV bit in CKGR_PLLBR (see

).

When the PLL B output is stable, i.e., the LOCKB is set:

• The USB host clock can be enabled by setting the UHP bit in PMC_SCER. To save power on

this peripheral when it is not used, the user can set the UHP bit in PMC_SCDR. The UHP bit

in PMC_SCSR gives the activity of this clock. The USB host port require both the 12/48 MHz

signal and the Master Clock. The Master Clock may be controlled via the Master Clock

Controller.

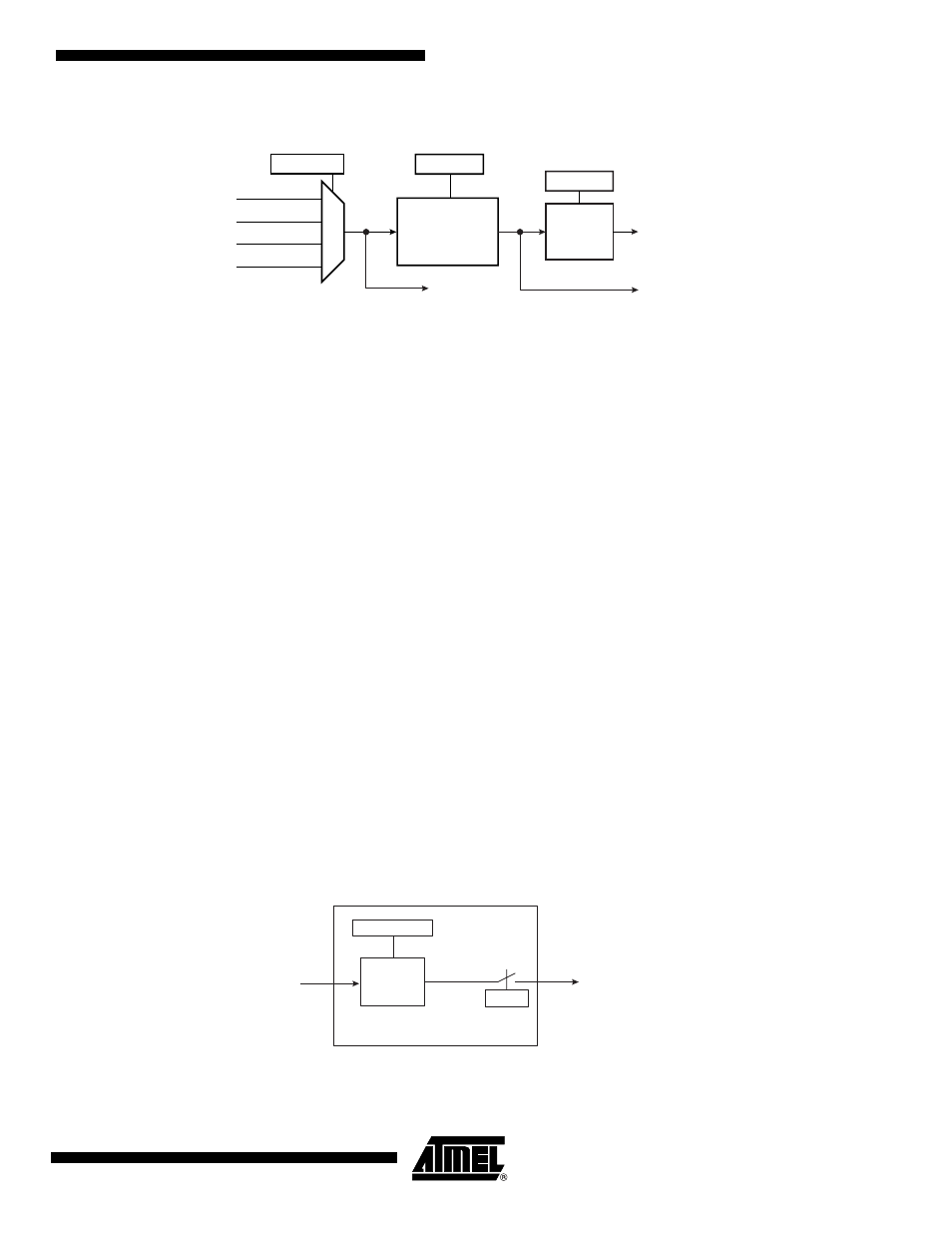

Figure 29-2. USB Clock Controller

SLCK

Master Clock

Prescaler

MCK

PRES

CSS

Master

Clock

Divider

MAINCK

PLLACK

PLLBCK

MDIV

To the Processor

Clock Controller (PCK)

PMC_MCKR

PMC_MCKR

PMC_MCKR

To the Double

Data Rate

Peripherals

(DDRCK)

USB

Source

Clock

UHP Clock (UHPCK)

UHP

USBDIV

Divider

/1,/2,/4