Rainbow Electronics AT91CAP9S250A User Manual

Page 282

282

6264A–CAP–21-May-07

AT91CAP9S500A/AT91CAP9S250A

an interrupt to signal the completion of the DMAC transfer. You can then re-program the channel

for a new DMAC transfer.

Single-buffer DMAC transfer: Consists of a single buffer.

Multi-buffer DMAC transfer: A DMAC transfer may consist of multiple DMAC buffers. Multi-

buffer DMAC transfers are supported through buffer chaining (linked list pointers), auto-reload-

ing of channel registers, and contiguous buffers. The source and destination can independently

select which method to use.

– Linked lists (buffer chaining) – A descriptor pointer (DSCR) points to the location

in system memory where the next linked list item (LLI) exists. The LLI is a set of

registers that describe the next buffer (buffer descriptor) and a descriptor pointer

register. The DMAC fetches the LLI at the beginning of every buffer when buffer

chaining is enabled.

– Replay – The DMAC automatically reloads the channel registers at the end of each

buffers to the value when the channel was first enabled.

– Contiguous buffers – Where the address of the next buffer is selected to be a

continuation from the end of the previous buffer.

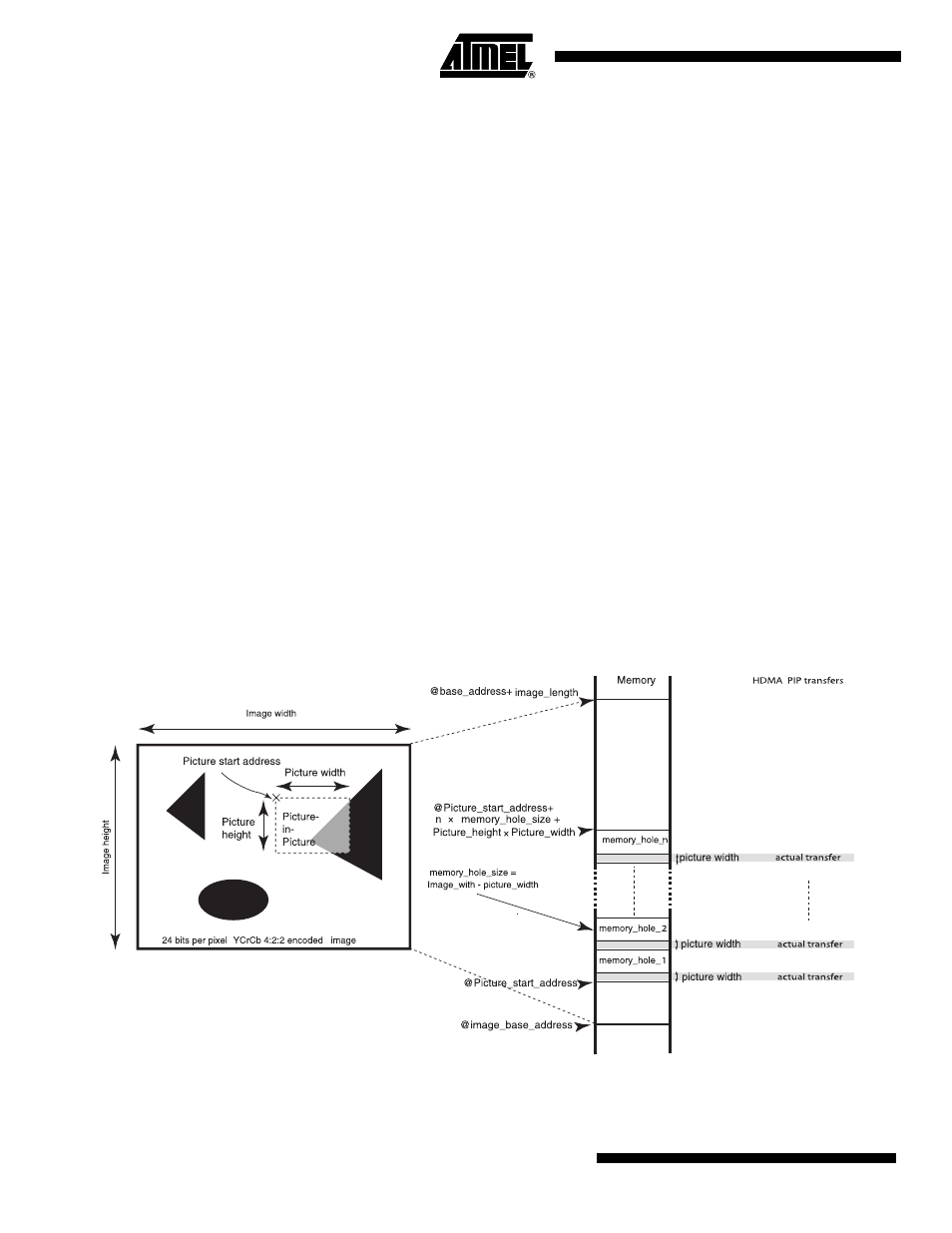

Picture-in-Picture Mode: DMAC contains a picture-in-picture mode support. When this mode is

enabled, addresses are automatically incremented by a programmable value when the DMAC

channel transfer count reaches a user defined boundary.

illustrates a memory mapped image 4:2:2 encoded located at

i m a g e _ b a s e _ a d d r e s s i n m e m o r y . A u s e r d e f i n e d s t a r t a d d r e s s i s d e f i n e d a t

Picture_start_address. The incremented value is set to memory_hole_size = image_width -

picture_width, and the boundary is set to picture_width.

Figure 26-5. Picture-In-Picture Mode Support

Channel locking: Software can program a channel to keep the AHB master interface by locking

the arbitration for the master bus interface for the duration of a DMAC transfer, buffer, or chunk.