Register: 0x07 – Avago Technologies LSI53C1000R User Manual

Page 147

SCSI Registers

4-35

Version 2.2

Copyright © 2000–2003 by LSI Logic Corporation. All rights reserved.

Register: 0x07

General Purpose (GPREG)

Read/Write

A write to this register causes the data written to be output to the

appropriate GPIO pin if it is set to output mode in the

General Purpose Pin Control (GPCNTL)

register.

To set the GPIO registers, follow these steps:

1.

Read the contents of the GPCNTL register.

2.

Read the contents of the GPREG register.

3.

Write the GPREG register.

4.

Write the GPCNTL register to control the pin for output/input.

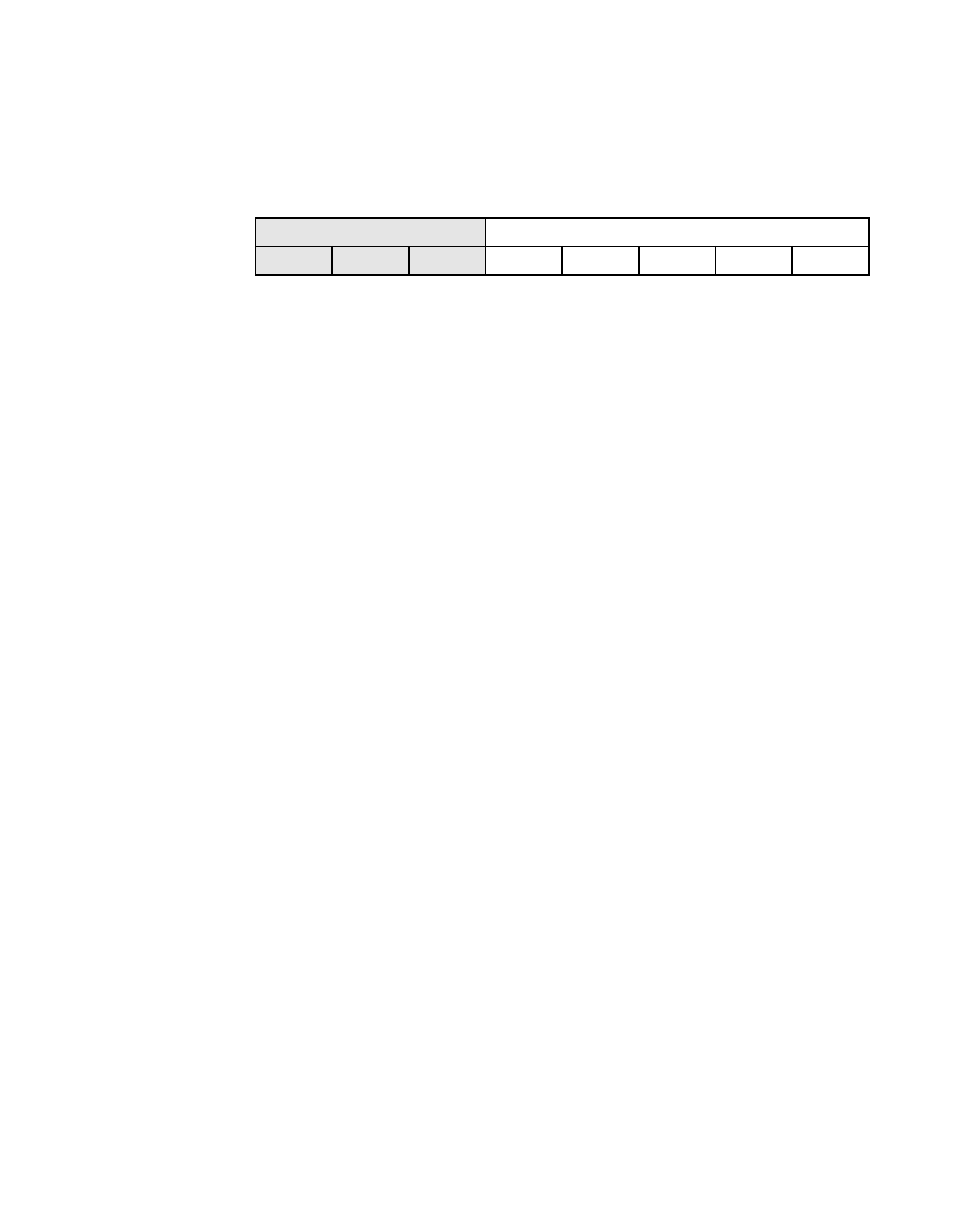

R

Reserved

[7:5]

GPIO

General Purpose I/O

[4:0]

These bits are programmed through the

General Purpose Pin Control (GPCNTL)

register as

inputs, outputs, or to perform special functions. As an

output, these pins can enable or disable external

terminators. It is also possible to program these signals

as live inputs and sense them through a SCRIPTS

register to register Move Instruction. GPIO[3:0] default as

inputs and GPIO4 defaults as an output pin. When

configured as inputs, an internal pull-up is enabled.

LSI Logic software uses the GPIO[1:0] signals to access

serial EEPROM. GPIO1 is used as a clock, with the

GPIO0 pin serving as data.

LSI Logic software also reserves the use of GPIO[4:2]. If

there is a need to use GPIO[4:2], check with LSI Logic for

additional information.

7

5

4

0

R

GPIO

x

x

x

0

x

x

x

x