2 address and data signals, Table 3.3 address and data signals, Address and data signals – Avago Technologies LSI53C1000R User Manual

Page 100

3-6

Signal Descriptions

Version 2.2

Copyright © 2000–2003 by LSI Logic Corporation. All rights reserved.

3.3.2 Address and Data Signals

describes the Address and Data Signals group.

Table 3.3

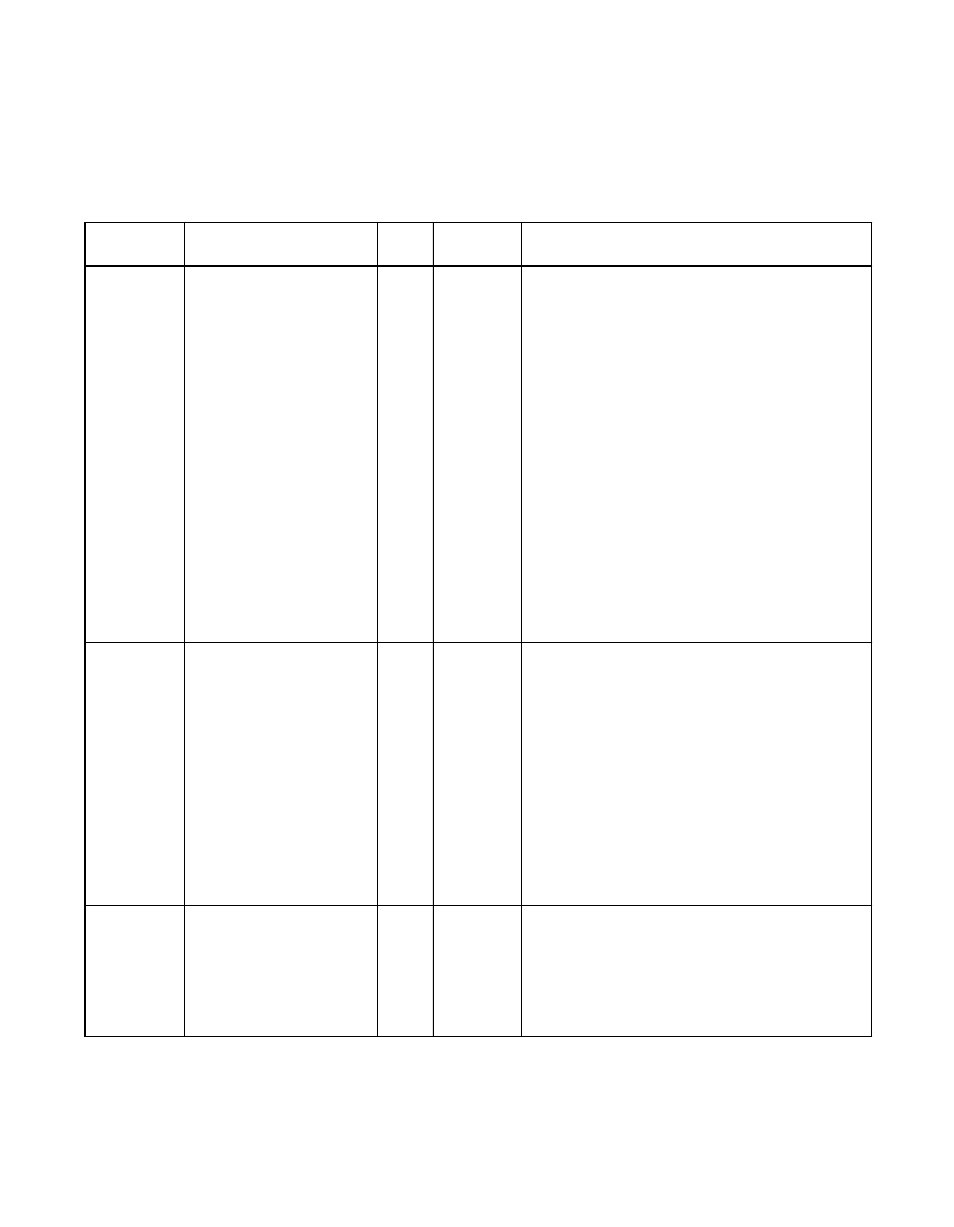

Address and Data Signals

Name

Bump

Type

Strength

Description

AD[63:0]

W22, AB25, AC26,

AA25, W23, Y25, Y26,

V22, U22, V24, V23,

U24, V25, W26, U23,

U25, T22, T23, T25,

R25, R22, P22, P23,

R23, P24, P25, T26,

R26, M26, L26, N25,

N24, AE9, AF8, AE10,

AB11, AC11, AE11,

AE12, AB12, AC12,

AD13, AE13, AF11,

AF16, AE14, AC15,

AC14, AD17, AE19,

AC18, AB17, AB18,

AF20, AE20, AC19,

AF23, AE22, AB19,

AD21, AF24, AC20,

AE23, AC21

T/S

8 mA PCI Physical longword Address and Data are

multiplexed on the same PCI pins. A bus

transaction consists of an address phase

followed by one or more data phases.

During the first clock of a transaction,

AD[63:0] contain a 64-bit physical byte

address. If the command is a dual address

cycle (DAC), implying a 64-bit address,

AD[31:0] contain the upper 32 bits of the

address during the second clock of the

transaction. During subsequent clocks,

AD[63:0] contain data. PCI supports both

read and write bursts. AD[7:0] define the

least significant byte, and AD[63:56] define

the most significant byte.

C_BE[7:0]/

AA23, AC25, Y23,

AD26, AB13, AB14,

AE18, AE21

T/S

8 mA PCI Bus Command and Byte Enables are

multiplexed on the same PCI pins. During

the address phase of a transaction,

C_BE[3:0]/ define the bus command. If the

transaction is a DAC, C_BE[3:0]/ contain the

DAC command and C_BE[7:4]/ define the

bus command. C_BE[3:0]/ define the bus

command during the second clock of the

transaction. During the data phase,

C_BE[7:0]/ are used as byte enables. The

byte enables determine which byte lanes

carry meaningful data: C_BE[0]/ applies to

byte 0 and C_BE[7] applies to byte 7.

PAR

AF19

T/S

8 mA PCI Parity is the even parity bit that protects the

AD[31:0] and C_BE[3:0]/ lines. During the

address phase, both the address and

command bits are covered. During the data

phase, both the data and byte enables are

covered.