Power management capabilities (pmc), Next item pointer (nip), Capability id (cid) – Avago Technologies LSI53C1000R User Manual

Page 130: Register: 0x40, Register: 0x41

4-18

Registers

Version 2.2

Copyright © 2000–2003 by LSI Logic Corporation. All rights reserved.

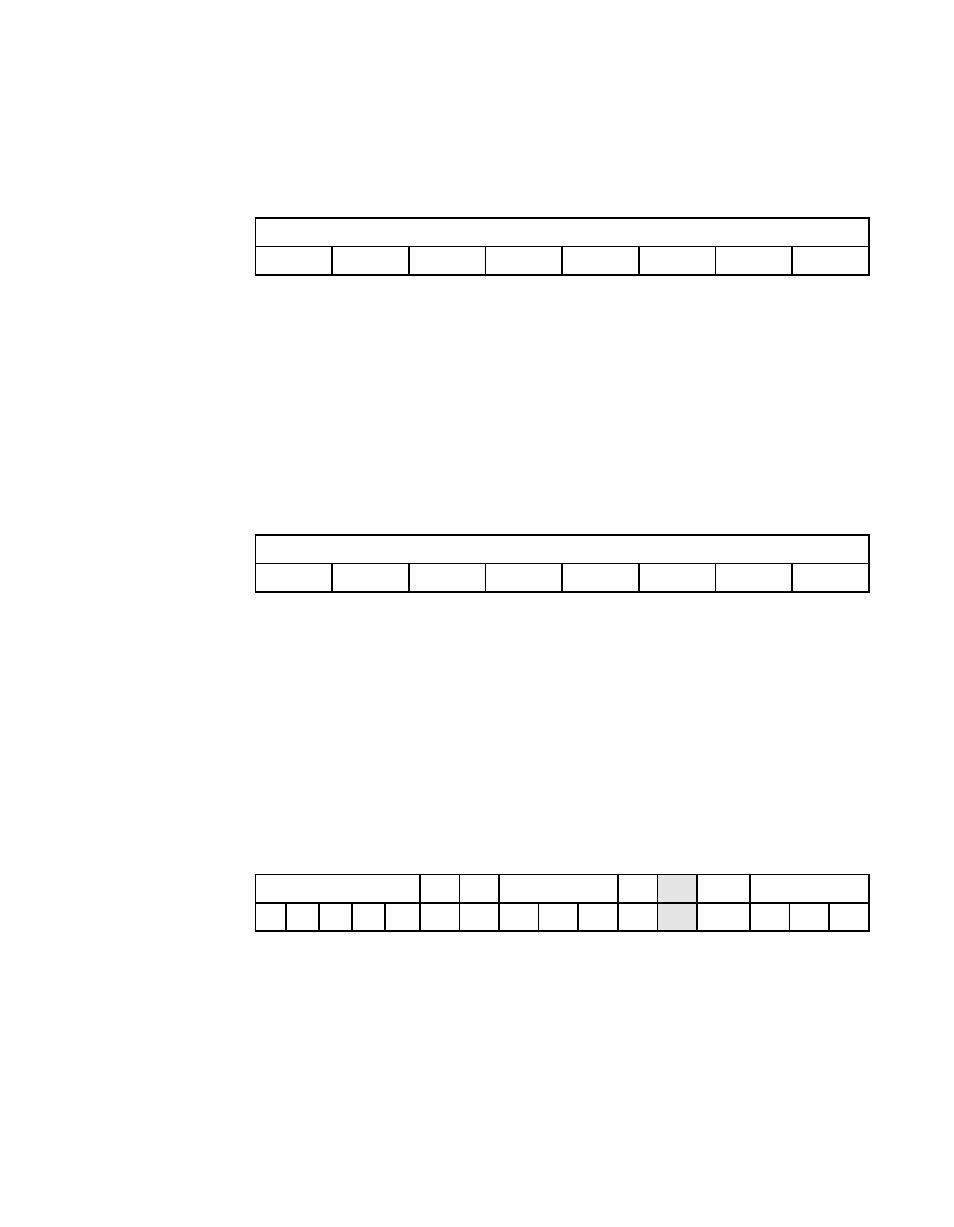

Register: 0x40

Capability ID (CID)

Read Only

CID

Capability ID

[7:0]

This register indicates the type of data structure currently

being used. It is set to 0x01, indicating the

Power Management Data Structure.

Register: 0x41

Next Item Pointer (NIP)

Read Only

NIP

Next Item Pointer

[7:0]

Bits [7:0] contain the offset location of the next item in the

function’s capabilities list. The LSI53C1000R has these

bits set to zero indicating no further extended capabilities

registers exist.

Registers: 0x42–0x43

Power Management Capabilities (PMC)

Read Only

PMES

PME_Support

[15:11]

Bits [15:11] define the power management states in

which the LSI53C1000R asserts the PME pin. These bits

are all set to zero because the LSI53C1000R does not

provide a PME signal.

7

0

CID

0

0

0

0

0

0

0

1

7

0

NIP

0

0

0

0

0

0

0

0

15

11

10

9

8

6

5

4

3

2

0

PMES

D2S D1S

AUX_C

DSI

R

PMEC

VER[2:0]

0

0

0

0

0

1

1

0

0

0

0

0

0

0

1

0