Scsi transfer (sxfer), Register: 0x05 – Avago Technologies LSI53C1000R User Manual

Page 145

SCSI Registers

4-33

Version 2.2

Copyright © 2000–2003 by LSI Logic Corporation. All rights reserved.

and

registers. The priority of

the 16 possible IDs, in descending order is:

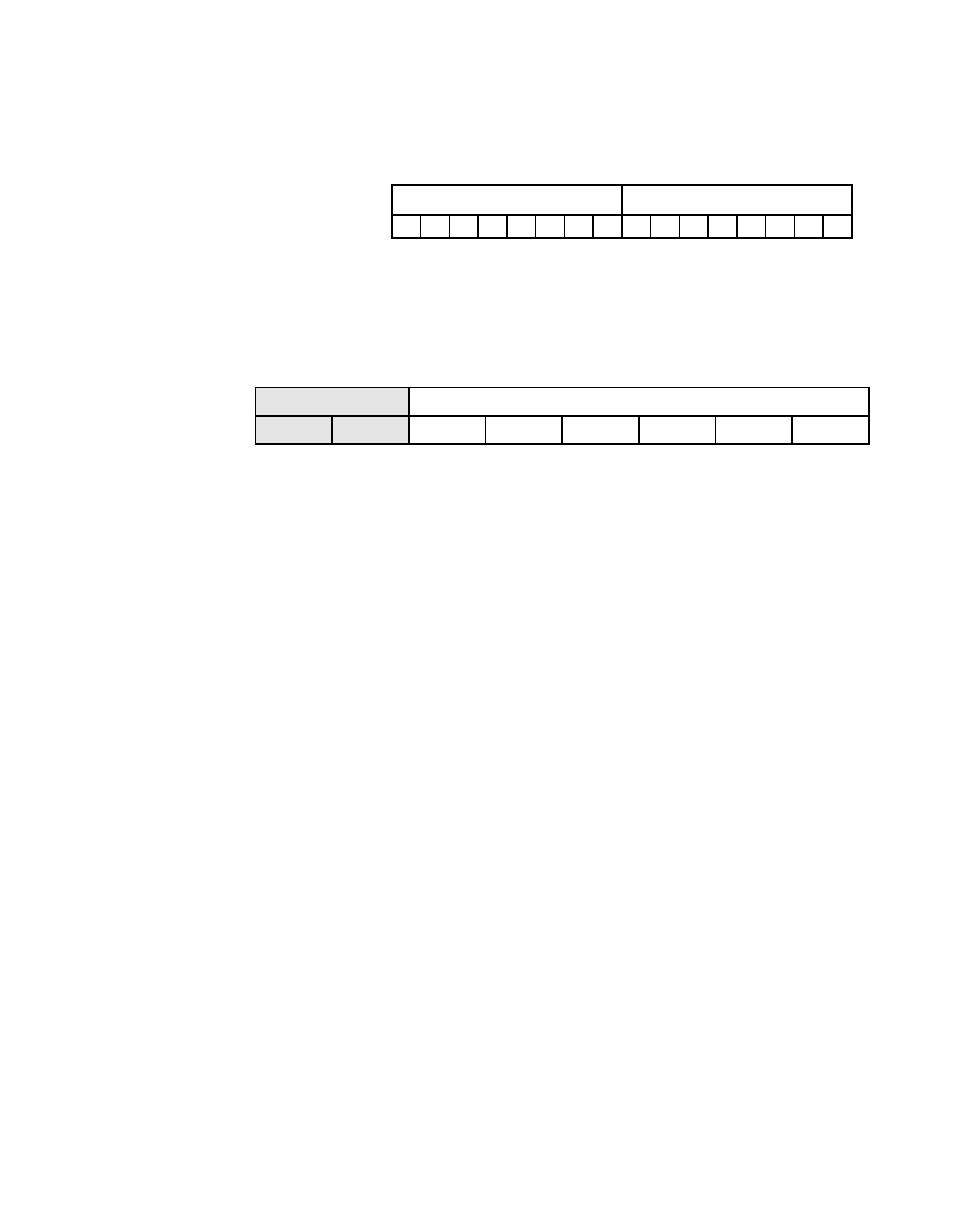

Register: 0x05

SCSI Transfer (SXFER)

Read/Write

This register is automatically loaded when a Table Indirect Select or

Reselect SCRIPTS instruction is executed.

R

Reserved

[7:6]

MO[5:0]

Max SCSI Synchronous Offset

[5:0]

These bits describe the maximum SCSI synchronous

offset used by the LSI53C1000R when transferring

synchronous SCSI data in either the initiator or target

mode.

describes the possible combinations and

their relationship to the synchronous data offset used by

the LSI53C1000R. These bits determine the

LSI53C1000R’s method of transfer for ST/DT Data-In and

ST/DT Data-Out phases only; all other information

transfers occur asynchronously. Note that the SCSI offset

for Ultra160 transfers is counted as the maximum number

of data transfers allowed to be outstanding, not the

maximum REQ pulses allowed to be outstanding.

During ST Data-In or ST Data-Out transfers the

maximum supported offset is 31 (MO[5:0] = 0x1F).

During DT Data-In or DT Data-Out transfers the

maximum supported offset is 62 (MO[5:0] = 0x3E).

Setting offset values outside the allowable range results

in data corruption.

A value of 0 in these bits program the device to perform

asynchronous transfers. A value of 1 during DT transfers

is illegal and results in data corruption.

Highest

Lowest

7

6

5

4

3

2

1

0 15 14 13 12 11 10 9

8

7

6

5

0

R

MO[5:0]

0

0

0

0

0

0

0

0