Rockwell Automation 1747-PT1, D1747NP002 Hand-Held Terminal User Manual

Page 459

Instruction Execution Times

Appendix C

Memory Usage,

C–5

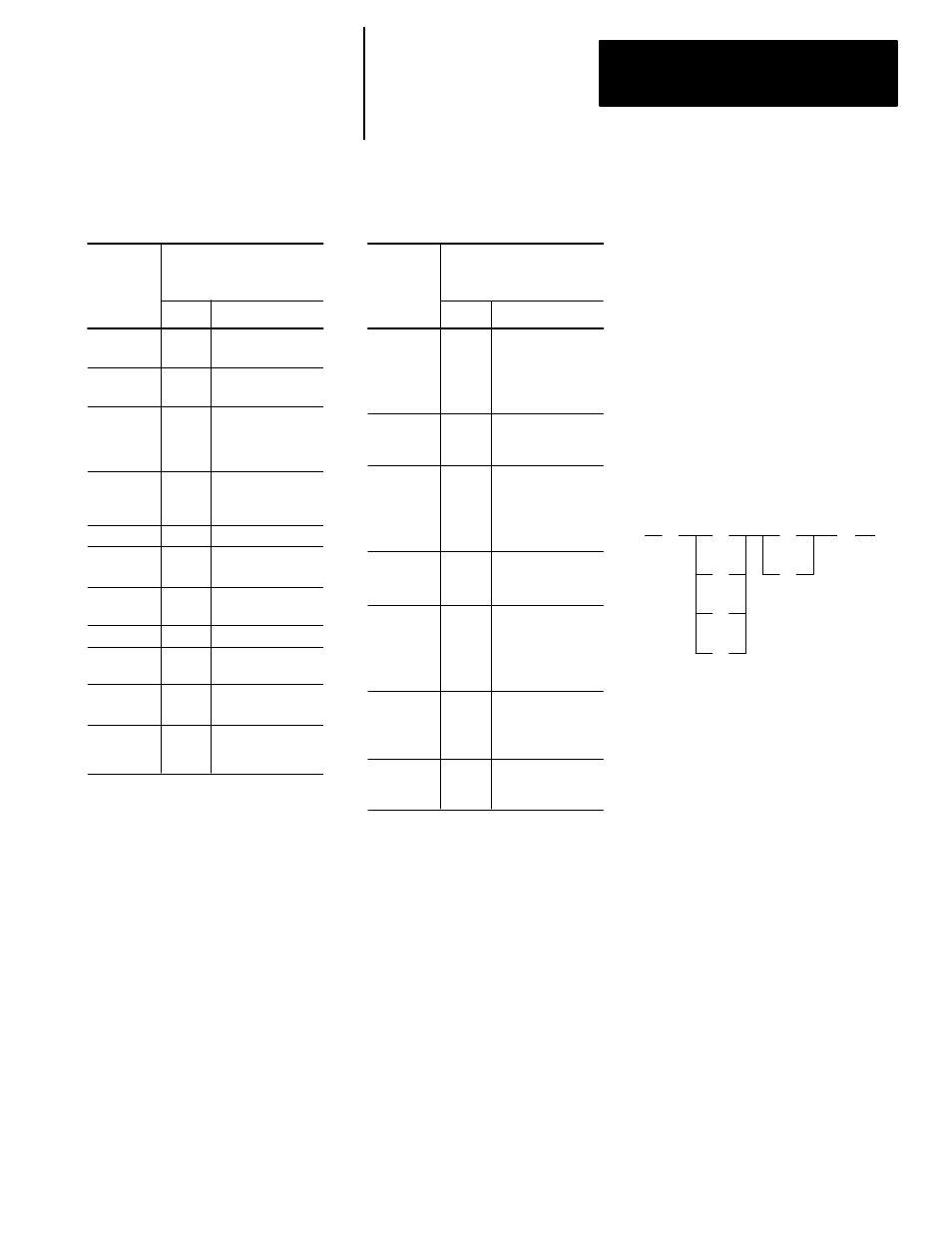

Instruction Execution Times for the Fixed and SLC 5/01 Processors

➀

Execution Time

in Microseconds

(approx.)

False

True

Instruction

ADD

12

122

AND

12

87

BSL

12

144 + 24 per word

BSR

12

134 + 24 per word

CLR

12

40

COP

12

45 + 21 per word

CTD

12

111

CTU

12

111

DCD

12

80

DDV

12

650

DIV

12

400

EQU

➀

12

60

FLL

12

37 +14 per word

FRD

12

223

GEQ

➀

12

60

GRT

➀

12

60

HSC

12

60

IIM

12

372

IOM

12

475

JMP

12

38

JSR

12

46

LBL

2

2

LEQ

➀

12

60

LES

➀

12

60

Execution Time

in Microseconds

(approx.)

False

True

Instruction

MCR

10

10

MEQ

➀

12

75

MOV

12

20

MUL

12

230

MVM

12

115

NEG

12

110

NEQ

➀

12

60

NOT

12

66

OR

12

87

OSR

12

34

OTE

18

18

OTL

19

19

OTU

19

19

RES

12

40

RET

12

34

RTO

12

140

SBR

2

2

SQC

12

225

SQO

12

225

SUB

12

125

SUS

12

12

TND

12

32

TOD

12

200

TOF

12

140

TON

12

135

XIC

➀

4

4

XIO

➀

4

4

XOR

12

87

For the rung example at the right:

1) If instruction 1 is false, instructions 2, 3,

4, 5, 6, 7 take zero execution time.

Execution time =

4 + 18 = 22 microseconds.

2) If instruction 1 is true, 2 is true, and 6 is

true, then instructions 3, 4, 5, 7 take

zero execution time. Execution time =

4 + 4 + 4 + 18 = 30 microseconds.

] [

1

( )

8

] [

2

] [

6

] [

3

] [

4

] [

5

] [

7

These instructions take zero execution time if

they are preceded by conditions that guarantee

the state of the rung. Rung logic is solved left

to right. Branches are solved top to bottom.

- 20P PowerFlex DC Drive - Frame D Bimetal Thermostat (10 pages)

- 1336S_F_T_E_R F Frame Snubber Resistor Repl. (6 pages)

- 22-COMM PowerFlex 4-Class DSI (Drive Serial Interface) Network Communication Adapter (4 pages)

- 8-545 Plug In Solid State Relay (2 pages)

- 20-HIM-B1 PowerFlex 7-Class HIM Bezel (DPI) (4 pages)

- 100 Contactors with DC Coil (2 pages)

- 100 Contactors with DC Coil (1 page)

- 20P PowerFlex DC Drive - Frame D Switching Power Supply Circuit Board (6 pages)

- 140G-MTFx_MTHx_MTIx_MTKx Trip Unit Installation-140G-M (6 pages)

- 45BRD Analog Laser Sensor (4 pages)

- 20D Multi-Device Interface Option Board for PowerFlex 700S Drives (20 pages)

- 56RF RFID 18 mm Cylindrical Transceiver (2 pages)

- 42KC Miniature Rectangular: 5V DC Version (2 pages)

- 20P PowerFlex DC Drive - Frame A Switching Power Supply Circuit Board (16 pages)

- 21P-MISC-A-TP-2 Transition Tube Kit #C19-6/7 For PowerFlex 755 w/OEM Liquid Cooling Fr 6/7 Drive (2 pages)

- 42BT Background Suppression Sensor (3 pages)

- 42CB High Speed 18mm Cylindrical (4 pages)

- 140EX-JE2_JE3 Molded Case Circuit Breaker (4 pages)

- 140G-K-EAM1A Early Make Aux Contact for Rotary Handle Oper Mech-140G-K (1 page)

- 140G-K-EAM1A Early Make Aux Contact for Rotary Handle Oper Mech-140G-K (3 pages)

- 20-HIM-A6 PowerFlex (Human Interface Module) (74 pages)

- 42CF General Purpose 12mm Cylindrical (4 pages)

- 20D PowerFlex 700S Phase II Drive Frames 1...6 (80 pages)

- 140EX-HE1_HE2 Molded Case Circuit Breaker (6 pages)

- 140EX-HE1_HE2 Molded Case Circuit Breaker (4 pages)

- 20B PowerFlex 700 Custom Firmware - Pump Off (12 pages)

- 20-WIM-N4S DPI Wireless Interface Module (92 pages)

- 140U H-Frame Circuit Breaker Fixed and Adjustable Thermal Trip (2 pages)

- 140U H-Frame Circuit Breaker Fixed and Adjustable Thermal Trip (7 pages)

- 60-2619, 42JS Swivel/Tilt Mounting Bracket (1 page)

- 22A PowerFlex 4/40/400 Flange Mount (4 pages)

- 45MLA Controller Installation Instructions (16 pages)

- 20P PowerFlex DC Drive - Cooling Fan for Frame A Drives Above 73A at 230V 460V AC (6 pages)

- 42JS Series 7000 to 42JS VisiSight Replacement Kit (2 pages)

- 22A PowerFlex 4-Class HIM Bezel (DSI) (4 pages)

- 42CS Stainless Steel Photoelectric Sensors (4 pages)

- 20L-LL PowerFlex 700L Liquid-to-Liquid Heat Exchanger (40 pages)

- 20P PowerFlex DC Drive - Frame B SCR Modules (20 pages)

- 22B PowerFlex 40 Quick Start FRN 5.xx - 6.xx (161 pages)

- 22B PowerFlex 40 Quick Start FRN 5.xx - 6.xx (22 pages)

- 22F PowerFlex 4M Input RFI Filters (2 pages)

- 45LFM Capacitive Label Sensor (4 pages)

- 140G-Rx Installation Instruction-140G-R (2 pages)

- 140G-Rx Installation Instruction-140G-R (29 pages)

- 22C PowerFlex 400 AC Drive Quick Start - FRN 1-4.xx (28 pages)