Rockwell Automation 1747-PT1, D1747NP002 Hand-Held Terminal User Manual

Page 382

Chapter 27

The Status File

27–14

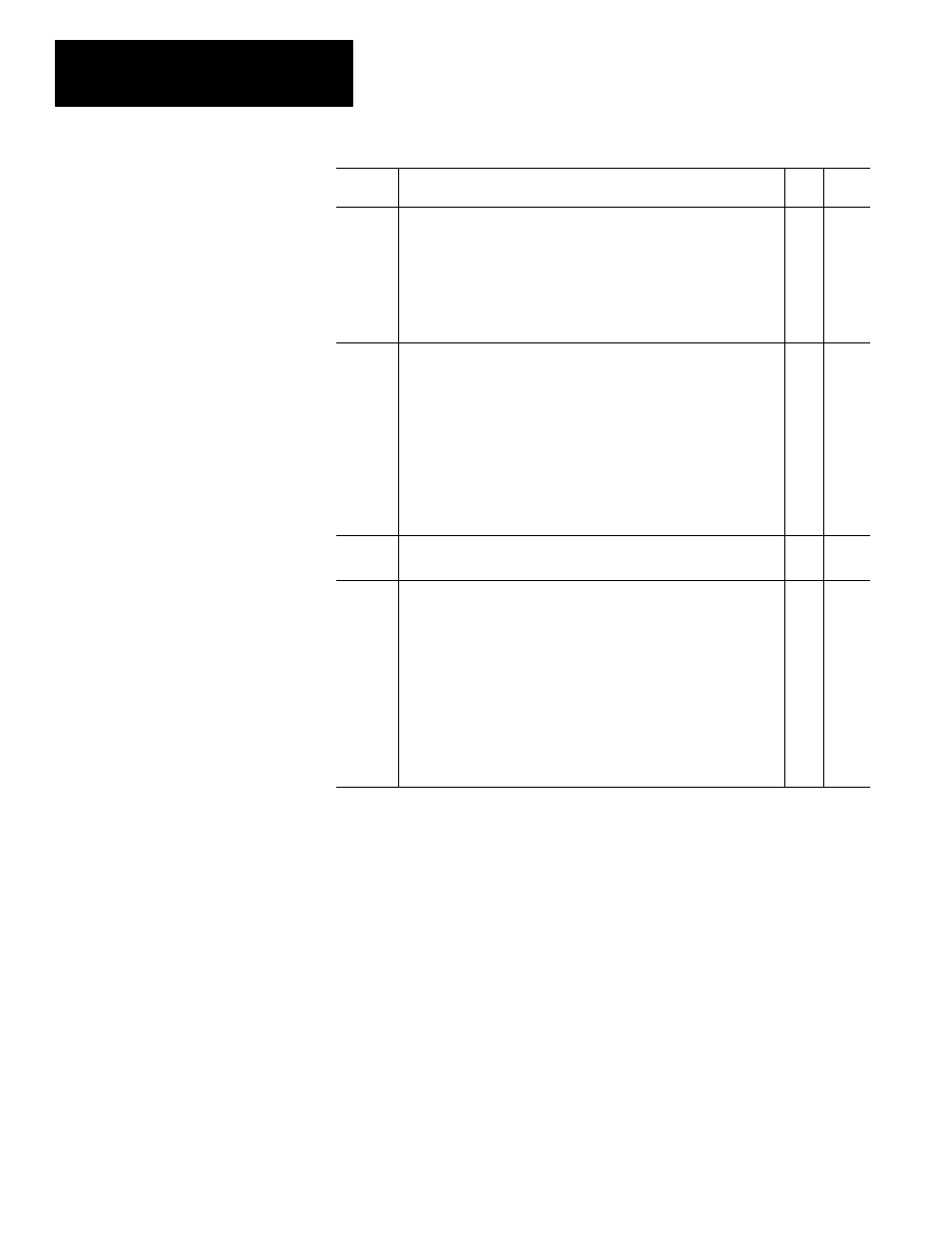

Address

Description

5/02

5/01,

Fixed

S:5

Minor Error Bits

The bits of this word are set by the processor to indicate that a minor

error has occurred in your ladder program. Minor errors, bits 0–7,

revert to major error 0020H if any bit is detected as being set at the

end of the scan. If the processor faults for error code 0020H, you

must clear minor error bits S:5/0–7 along with S:1/13 to attempt error

recovery.

•

•

S:5/0

Overflow Trap Bit

Read/write. When this bit is set by the processor, it indicates that a

mathematical overflow has occurred in the ladder program (see

S:0/1).

If this bit is ever set upon execution of the END, TND, or REF

instruction, a major error (0020) will be declared. To avoid this type of

major error from occurring, examine the state of this bit following a

math instruction (ADD, SUB, MUL, DIV, DDV, NEG, SCL, TOD, or

FRD), take appropriate action, and then clear bit S:5/0 using an OTU

instruction with S:5/0 or a CLR instruction with S:5.0.

•

•

S:5/1

Reserved

•

•

S:5/2

Control Register Error Bit

Read/write. The LFU, LFL, FFU, FFL, BSL, BSR, SQO, SQC, and

SQL instructions are capable of generating this error. When bit S:5/2

is set, it indicates that the error bit ER of the control instruction has

been set.

If this bit is ever set upon execution of the END, TND, or REF

instruction, a major error (0020) will be declared. To avoid this type of

major error from occurring, examine the state of this bit following a

control register instruction, take appropriate action, and then clear bit

S:5/2 using an OTU instruction with S:5/2 or a CLR instruction with

S:5.0.

•

•