Rockwell Automation 1747-PT1, D1747NP002 Hand-Held Terminal User Manual

Page 240

Chapter 17

Timer and Counter Instructions

17–8

Status Bits

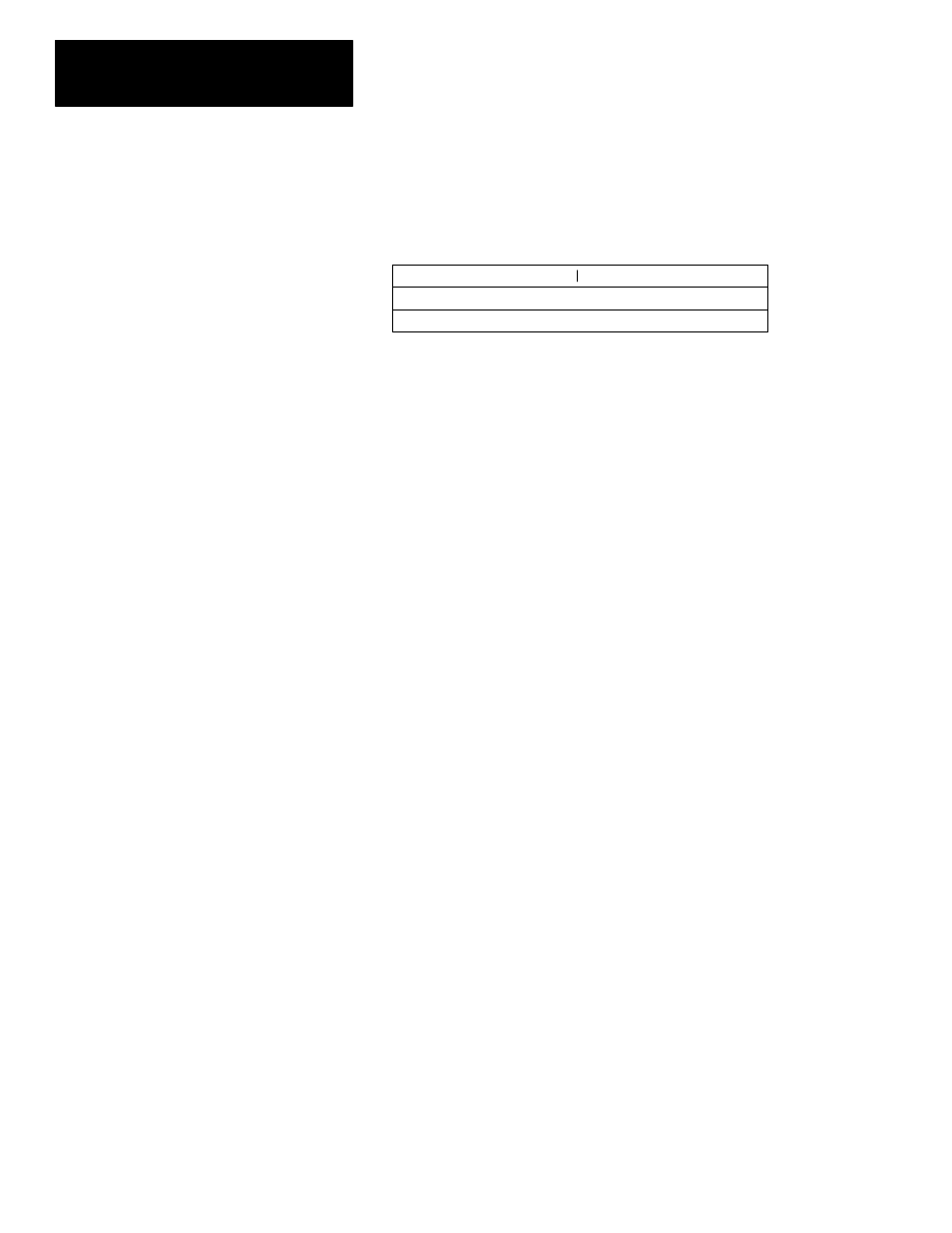

The control word for counter instructions includes six status bits, indicated in

the figure below.

CU CD DN OV UN UA Not Used

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Preset Value

Accumulated Value

CU = Counter up enable bit

CD = Counter down enable bit

DN = Done bit

OV = Overflow bit

UN = Underflow bit

UA = Update accumulator (HSC only)

Counter preset and accumulated values are stored as signed integers.

Negative values are stored in two’s complementary form.

When rung conditions for a CTU instruction have a false-to-true transition,

the accumulated value increments by one count, provided that an evaluation

occurs between these transitions. When this occurs successively so that the

accumulated value becomes equal to the preset value, the counter done (DN)

bit is set and remains set if the accumulator exceeds the preset.

Bit 15 of the counter control word is the count up enable (CU) bit. It is set

when rung conditions of the CTU instruction are true. The bit is reset when

either rung conditions go false or an RES instruction having the same address

as the CTU instruction is enabled.

CTU instructions can count beyond their preset value. When counting

continues past the preset value and reaches (32,767 + 1), an overflow

condition results. This is indicated when bit 12, the overflow (OV) bit, is set.

You can reset the overflow bit by enabling a RES instruction having the same

address as the CTU instruction. You can also reset the overflow bit by

decrementing the count less than or equal to 32,767 with a CTD instruction.

When the OV bit is set, the accumulated value wraps around to – 32,768 and

continues counting up from there.