Double divide (ddv), Using arithmetic status bits – Rockwell Automation 1747-PT1, D1747NP002 Hand-Held Terminal User Manual

Page 285

Chapter 20

Math Instructions

20–9

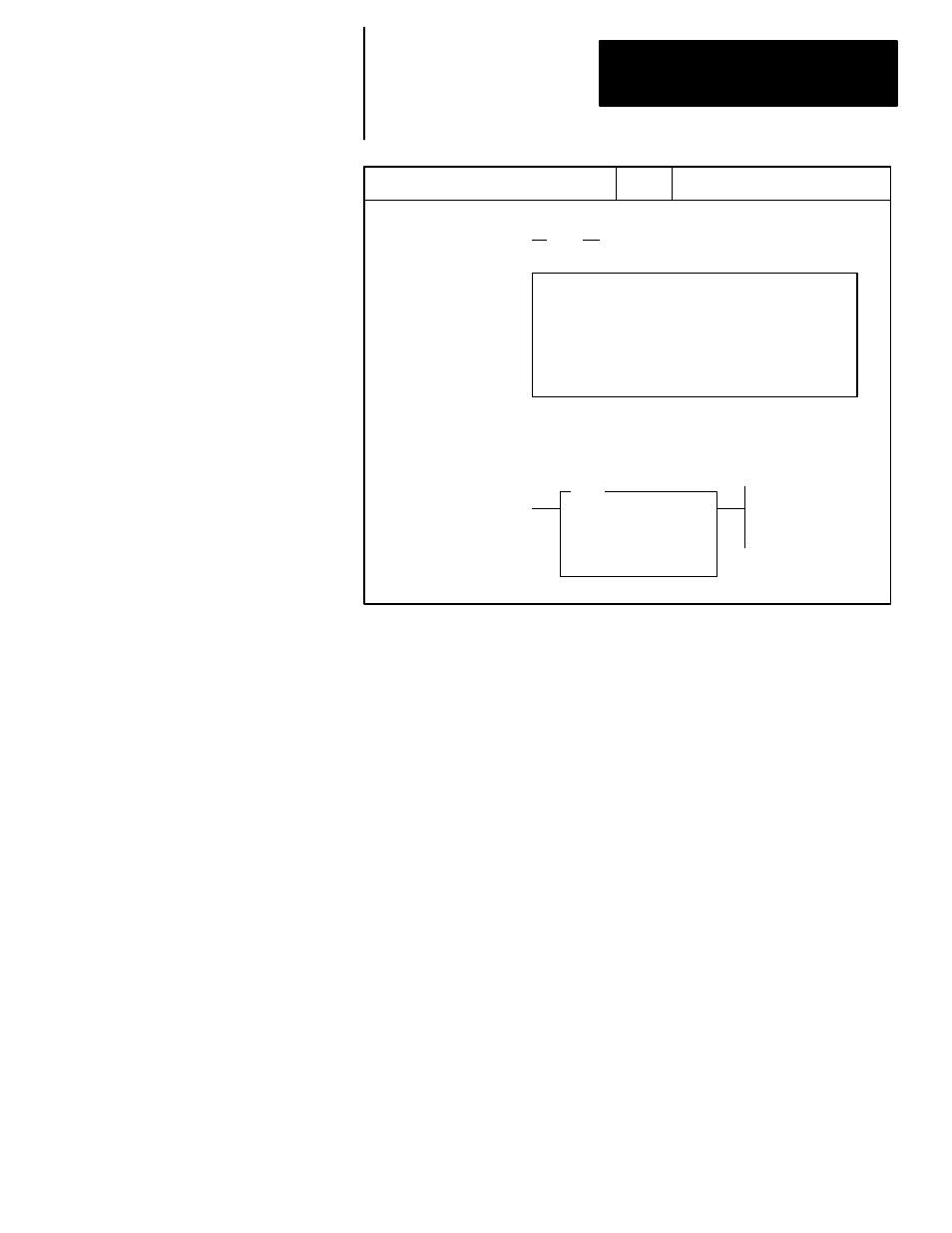

DDV

DOUBLE DIVIDE

Source

N7:0

9

Dest

N7:1

5000

Double Divide

DDV

Output Instruction

(DDV)

F1

F2

F3

F4

F5

ZOOM on DDV –(DDV)– 2.3.0.0.2

NAME: DOUBLE DIVIDE

SOURCE: N7:0 9

DEST: N7:1 5000

EDT_DAT

HHT Ladder Display:

HHT Zoom Display:

Ladder Diagrams and APS Displays:

(online monitor mode)

The contents of the math register are divided by the source value. The

rounded quotient is placed in the destination. If the remainder is 0.5 or

greater, round up occurs in the destination. The unrounded quotient is placed

in the most significant word of the math register. The remainder is placed in

the least significant word of the math register.

Using Arithmetic Status Bits

C always reset

V set if division by zero or if the result is greater than 32,767 or less than

–32,768; otherwise reset. On overflow, the minor error flag is also set.

The value 32,767 is placed in the destination.

Z set if the result is zero; otherwise reset

S set if the result is negative; otherwise reset; undefined if overflow is set

Math Register

Initially contains the dividend of the DDV operation. Upon instruction

execution the unrounded quotient is placed in the most significant word of

the math register. The remainder is placed in the least significant word of the

math register.

Double Divide (DDV)