Rockwell Automation 1747-PT1, D1747NP002 Hand-Held Terminal User Manual

Page 375

Chapter 27

The Status File

27–7

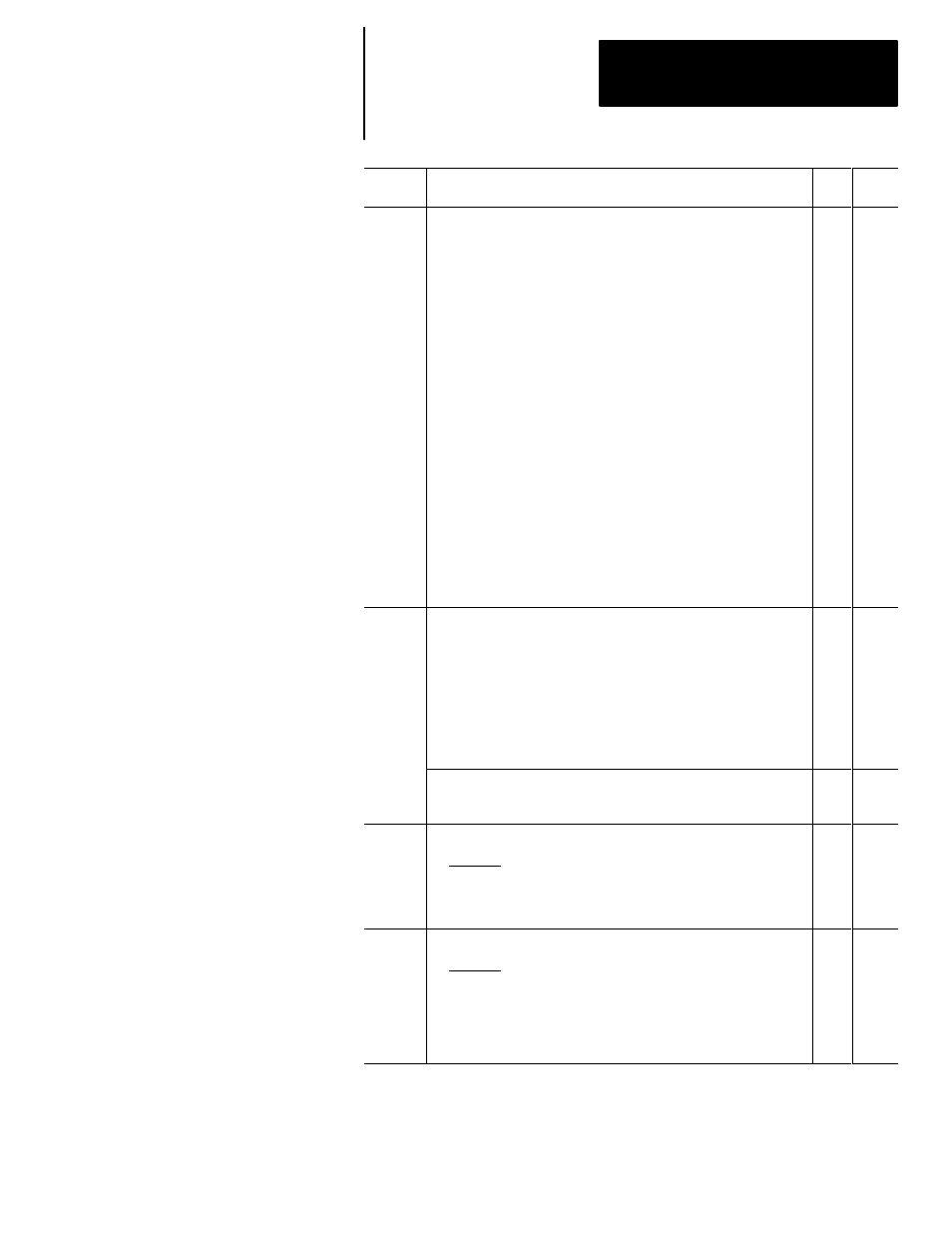

Address

Description

5/02

5/01,

Fixed

S:1/14

Access Denied Bit

Read/write. You can allow or deny future access to a processor file.

If you deny access, the processor sets this bit, indicating that a

programming device must have a matching copy of the processor file

in its memory in order to monitor the ladder program. A programming

device that does not have a matching copy of the processor file is

denied access.

To program this feature, select “Future Access Disallow” (SLC 5/02)

or “Future Access No” (SLC 5/01) when saving your program. To

provide protection from inadvertent data monitor alteration of your

selection, program an unconditional OTL instruction at address

S:1/14 to deny future access, or an unconditional OTU instruction at

address S:1/14 to allow future access.

When this bit is cleared, it indicates that any compatible programming

device can access the ladder program (provided that password

conditions are satisfied).

When access is denied, the programming device (APS, HHT) may

not display the ladder diagram or allow access to the EDT_DAT

function unless the device contains a matching copy of the processor

file. Functions such as change mode, clear memory, restore

program, and transfer memory module are allowed regardless of this

selection. A device such as the DTAM is not affected by this function.

•

•

S:1/15

First Pass Bit

Read/write. You can use this bit to initialize your program as the

application requires. When this bit is set by the processor, it indicates

that the first scan of the user program is in progress (following power

up in the Run mode or entry into a run or test mode). The processor

clears this bit following the first scan.

When this bit is cleared, it indicates that the program is not in the first

scan of a test or Run mode.

•

•

This bit will be set during execution of the startup protection fault

routine. See S:1/9.

•

S:2/0

STI (Selectable Timed Interrupt) Pending Bit

Read only. When set, this bit indicates that the STI timer has timed

out and the STI routine is waiting to be executed. This bit is cleared

upon starting of the STI routine, powerup, Run mode exit, or

execution of a true STS instruction.

•

S:2/1

STI (Selectable Timed Interrupt) Enabled Bit

Read only. This bit is set in its default condition, or when set by the

STE or STS instruction. If set, it allows execution of the STI if the STI

file (word 31) and STI rate (word 30) are non–zero. If clear when the

interrupt occurs, the STI subroutine does not execute and the STI

pending bit is set. The STI Timer continues to run when disabled.

The STI instruction clears this bit.

•