Rockwell Automation 1747-PT1, D1747NP002 Hand-Held Terminal User Manual

Page 232

Chapter 16

Bit Instructions

16–8

( )

O:3.0

0

]/[

B3

1

TOD

TO BCD

Source

T4:0.ACC

Dest

O:3

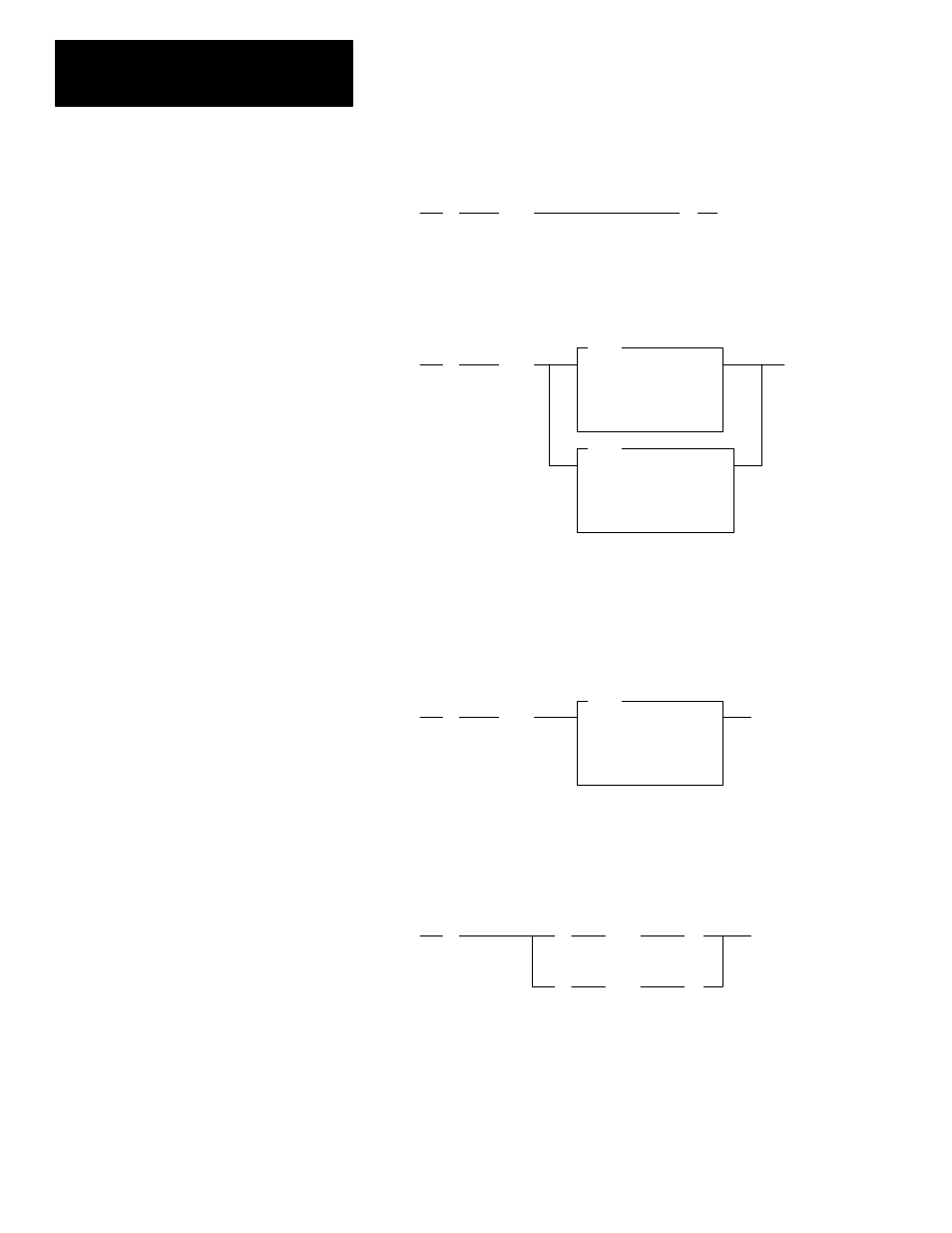

When the input instruction goes from false–to–true, the OSR instruction conditions the

rung so that the output goes true for one program scan. The output goes false and

remains false for successive scans until the input makes another false–to–true transition.

] [

I:1.0

0

[OSR]

B3

0

( )

O:3.0

0

[OSR]

B3

3

( )

O:3.0

1

] [

B3

2

] [

I:1.0

0

[OSR]

B3

0

] [

I:1.0

0

[OSR]

B3

0

SLC 5/02 Processors Only

This example is the same as the one above, except that a MOV instruction is not required.

The accumulated value of a timer is converted to BCD and moved to an output word

where an LED display is connected. When the timer is running, the accumulated value is

changing rapidly. This value can be frozen and displayed for each false–to–true transition

of the input condition of the rung.

Using the OSR instruction in output branching such as in this example is permitted when

using the SLC 5/02 processor. In this case, when I:1/0 is on, output O:3/0 will be on for

one scan only if B3/1 in not on, and output O:3/1 will be on for one scan only if B3/2 is on.

Fixed, SLC 5/01, SLC 5/02 Processors

TOD

TO BCD

Source

T4:0.ACC

Dest

S:13

] [

I:1.0

0

[OSR]

B3

0

MOV

MOVE

Source

S:13

Dest

O:3

In this case, the accumulated value of a timer is converted to BCD and moved to an

output word where an LED display is connected. When the timer is running, the

accumulated value is changing rapidly. This value can be frozen and displayed for each

false–to–true transition of the input condition of the rung.

The SLC 5/02 processor allows you to use one OSR instruction per output in

a rung. The SLC 5/01 processor allows you to use one OSR instruction per

rung. Do not place input conditions after the OSR instruction in a rung.

Unexpected operation may occur.