Rockwell Automation 1747-PT1, D1747NP002 Hand-Held Terminal User Manual

Page 376

Chapter 27

The Status File

27–8

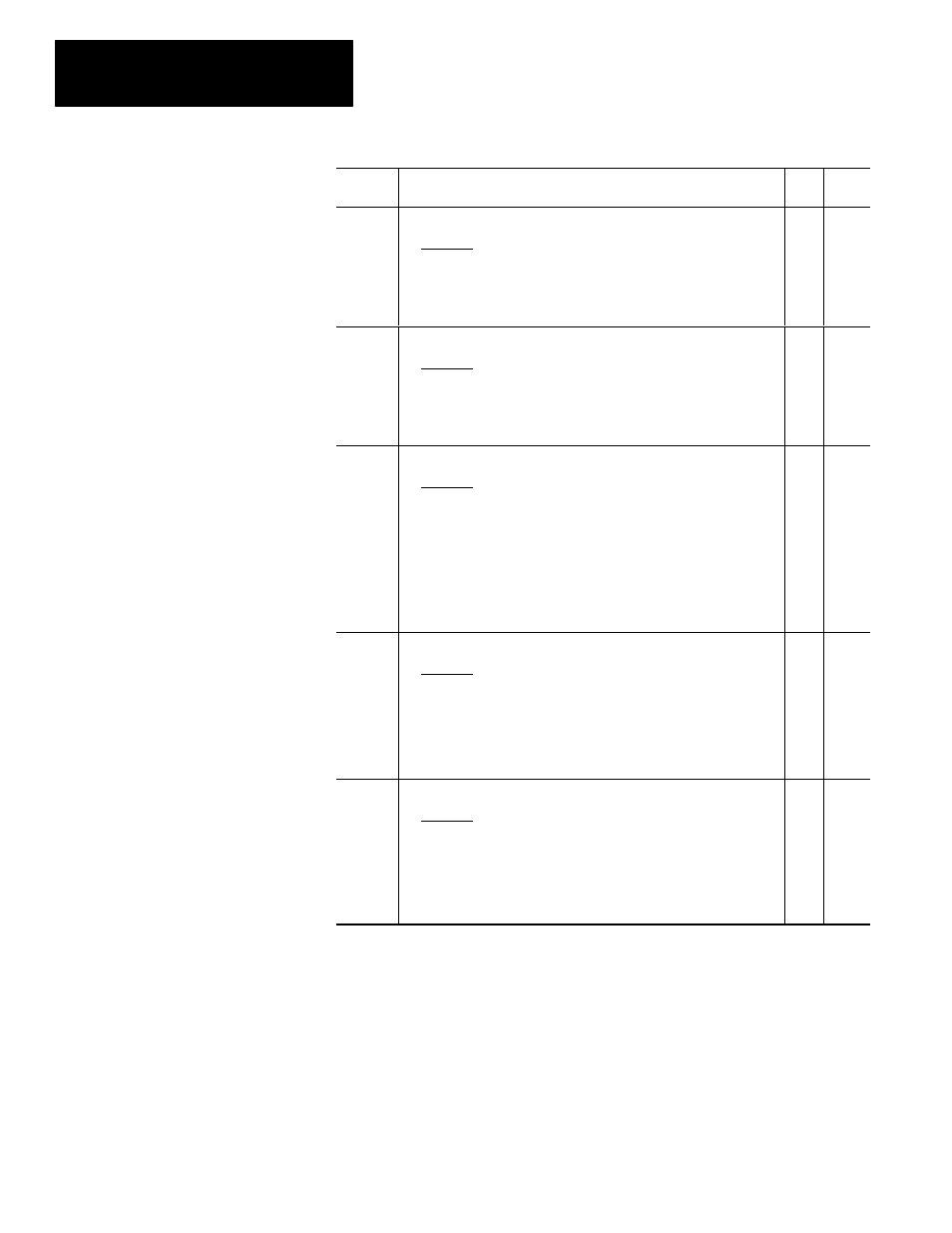

Address

Description

5/02

5/01,

Fixed

S:2/2

STI (Selectable Timed Interrupt) Executing Bit

Read only. This bit, when set, indicates that the STI timer has timed

out and the STI subroutine is currently being executed. Application

example: You could examine this bit in your fault routine to determine

if your STI was executing when the fault occurred. This bit is cleared

upon completion of the STI routine, powerup, or Run mode entry.

•

S:2/3

Index Addressing File Range Bit

Read only. Selected by the user at the time the user program is

saved. When clear, the index register can index only within the same

data file of the specified base address. When set, the index register

can index anywhere from data file B3:0 to the end of the last declared

data file.

•

S:2/4

Saved with Single Step Test Enabled Bit

Read only. This bit is selected by the user prior to saving the user

program. When clear, the Single Step Test mode function is not

available. Clear also indicates that debug registers S:16 through

S:21 are inoperative. When set, the program can operate in the

Single Step Test mode. See descriptions of S:16 through S:21.

When set, your program will also require 0.375 instruction words (3

bytes) per rung of additional memory.

Note: The HHT can save a SLC 5/02 program that has this option

enabled, but the Test Single Step mode is not available with the HHT.

•

S:2/5

DH–485 Incoming Command Pending Bit

Read only. This bit becomes set when the processor determines that

another node on the DH–485 network has requested information or

supplied a command to it. This bit can become set at any time. This

bit is cleared when the processor services the request (or command).

You can use this bit as a condition of an SVC instruction to enhance

the communications capability of your processor.

•

S:2/6

DH–485 Message Reply Pending Bit

Read only. This bit becomes set when another node on the DH–485

network has supplied the information that you have requested in the

MSG instruction of your processor. This bit is cleared when the

processor stores the information and updates your MSG instruction.

You can use this bit as a condition of an SVC instruction to enhance

the communications capability of your processor.

•