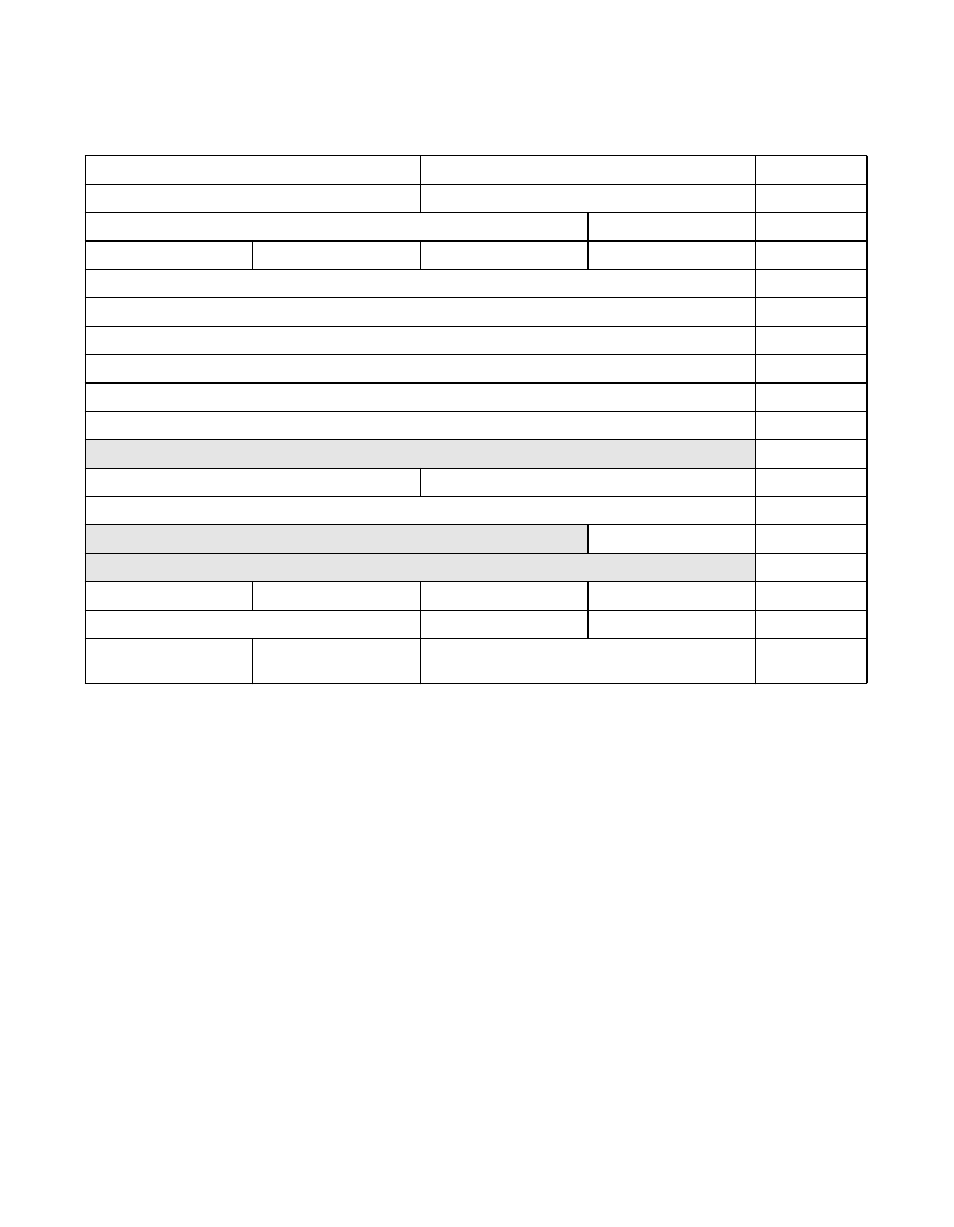

Table 3.2 pci configuration register map, Pci configuration register map, Table 3.2 – Avago Technologies LSI8751D User Manual

Page 76

3-12

PCI Functional Description

Table 3.2

PCI Configuration Register Map

31

16 15

0

Not Supported

1. I/O Base is supported.

2

2. Memory Base is supported.

Base Address Two (Memory) SCRIPTS RAM

3

3. This register powers up enabled and can be disabled by pull-down resistors on the MAD5 pin.

Not Supported

0x1C

Not Supported

0x20

Not Supported

0x24

Reserved

0x28

4

4. If expansion memory is enabled through pull-down resistors on the MAD[7:0] bus.

Note: Addresses 0x40–0x7F are not defined for the LSI53C875. Addresses 0x48–0x7F are not defined

for the LSI53C875E. All unsupported registers are not writable and return all zeros when read.

Reserved registers also return zeros when read.

Reserved

Reserved

0x38

This manual is related to the following products: