7 load and store instructions, Load and store instructions – Avago Technologies LSI8751D User Manual

Page 233

Load and Store Instructions

6-37

6.7 Load and Store Instructions

The Load and Store instructions provide a more efficient way to move

data from/to memory to/from an internal register in the chip without using

the normal memory move instruction.

The Load and Store instructions are represented by two Dword opcodes.

The first Dword contains the

and

register values. The second Dword contains the

value. This is either the actual memory

location of where to Load or Store, or the offset from the

, depending on the value of bit 28 (DSA Relative).

A maximum of 4 bytes may be moved with these instructions. The

register address and memory address must have the same byte

alignment, and the count set such that it does not cross Dword

boundaries. The destination memory address in the Store instruction and

the source memory address of the Load instruction may not map back

to the operating register set of the chip. This excludes the SCRIPTS

RAM and ROM memory spaces. If it does, a PCI read/write cycle occurs

(the data does not actually transfer to/from the chip), and the chip issues

an interrupt (Illegal Instruction Detected) immediately following.

The SIOM and DIOM bits in the

register determine

whether the destination or source address of the instruction is in Memory

space or I/O space, as illustrated in the following table. The Load and

Store utilizes the PCI commands for I/O read and I/O write to access the

I/O space.

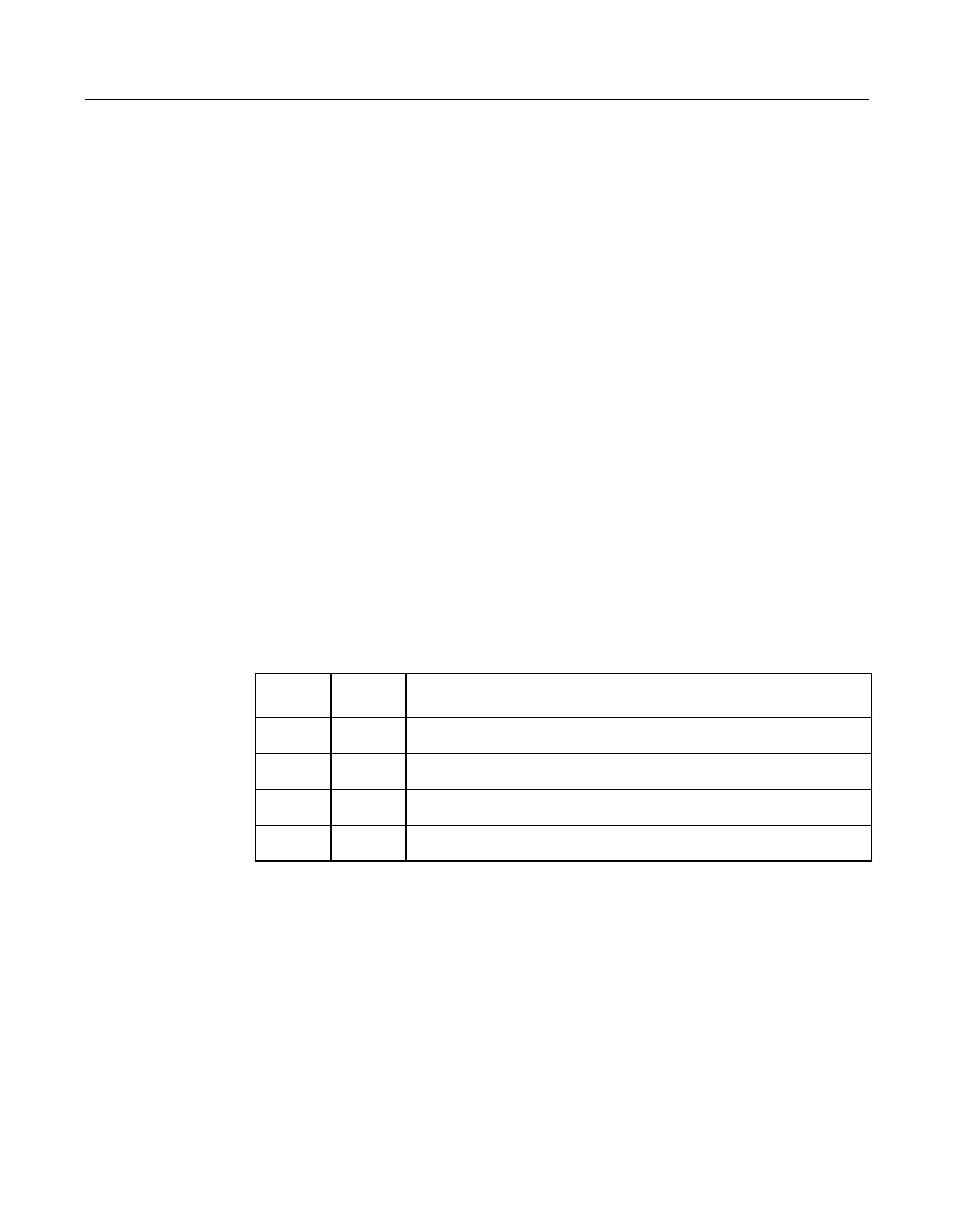

Bit A1

Bit A0

Number of Bytes Allowed to Load and Store

0

0

One, two, three or four

0

1

One, two, or three

1

0

One or two

1

1

One