Bits used for parity control and generation, Table 2.2 – Avago Technologies LSI8751D User Manual

Page 37

PCI Cache Mode

2-13

slave write operations causes a fatal DMA interrupt; SCRIPTS stops

running. Mask this interrupt with the EBPE Interrupt Enable bit, bit 1 in

the

register. These additional parity pins in

no way affect the generation or checking of the PCI specified parity line.

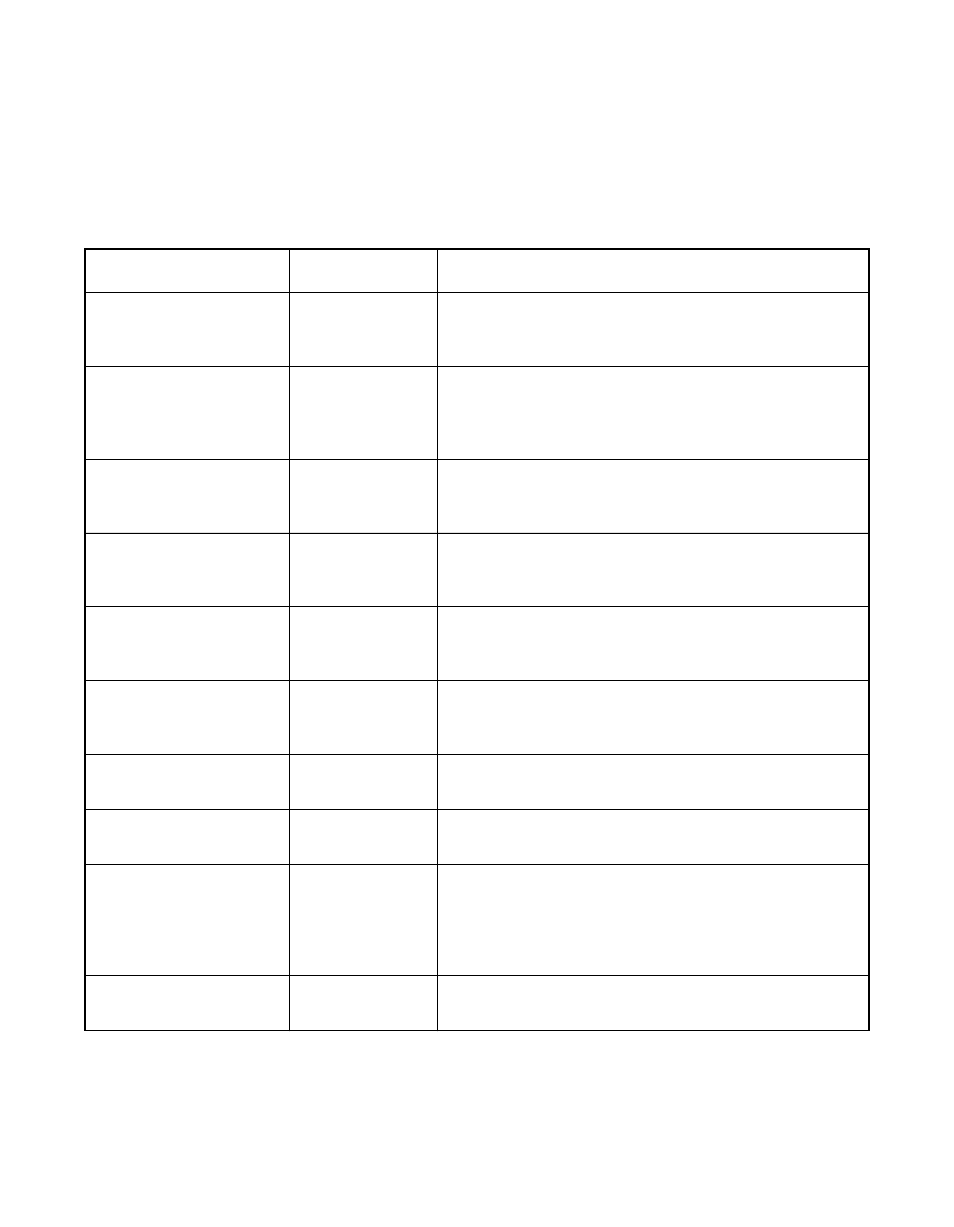

Table 2.2

Bits Used for Parity Control and Generation

BIt Name

Location

Description

Assert SATN/ on Parity

Errors

,

Bit 1

When this bit is set, the LSI53C875 automatically

asserts the SATN/ signal upon detection of a parity

error. SATN/ is only asserted in initiator mode.

Enable Parity Checking

,

Bit 3

Enables the LSI53C875 to check for parity errors. The

LSI53C875 checks for odd parity. This bit also checks

for parity errors on the four additional parity pins on the

LSI53C875N.

Assert Even SCSI Parity

Bit 2

Determines the SCSI parity sense generated by the

LSI53C875 to the SCSI bus.

Disable Halt on SATN/

or a Parity Error (Target

Mode Only)

Bit 5

Causes the LSI53C875 not to halt operations when a

parity error is detected in target mode.

Enable Parity Error

Interrupt

SCSI Interrupt

Enable Zero

(SIEN0)

, Bit 0

Determines whether the LSI53C875 generates an

interrupt when it detects a SCSI parity error.

Parity Error

SCSI Interrupt

Status Zero

(SIST0)

, Bit 0

This status bit is set whenever the LSI53C875 has

detected a parity error on the SCSI bus.

Status of SCSI Parity

Signal

, Bit 0

This status bit represents the active HIGH current state

of the SCSI SDP0 parity signal.

SCSI SDP1 Signal

, Bit 0

This bit represents the active HIGH current state of the

SCSI SDP1 parity signal.

Latched SCSI Parity

, Bit 3

and

,

Bit 3

These bits reflect the SCSI odd parity signal

corresponding to the data latched into the

register.

Master Parity Error

Enable

, Bit 3

Enables parity checking during master data phases.