Table 3.1 pci bus commands and encoding types, Pci bus commands and encoding types, Table 3.1 – Avago Technologies LSI8751D User Manual

Page 67

PCI Addressing

3-3

3.1.1.1 I/O Read Command

The I/O Read command reads data from an agent mapped in I/O

address space. All 32 address bits are decoded.

3.1.1.2 I/O Write Command

The I/O Write command writes data to an agent when mapped in I/O

address space. All 32 address bits are decoded.

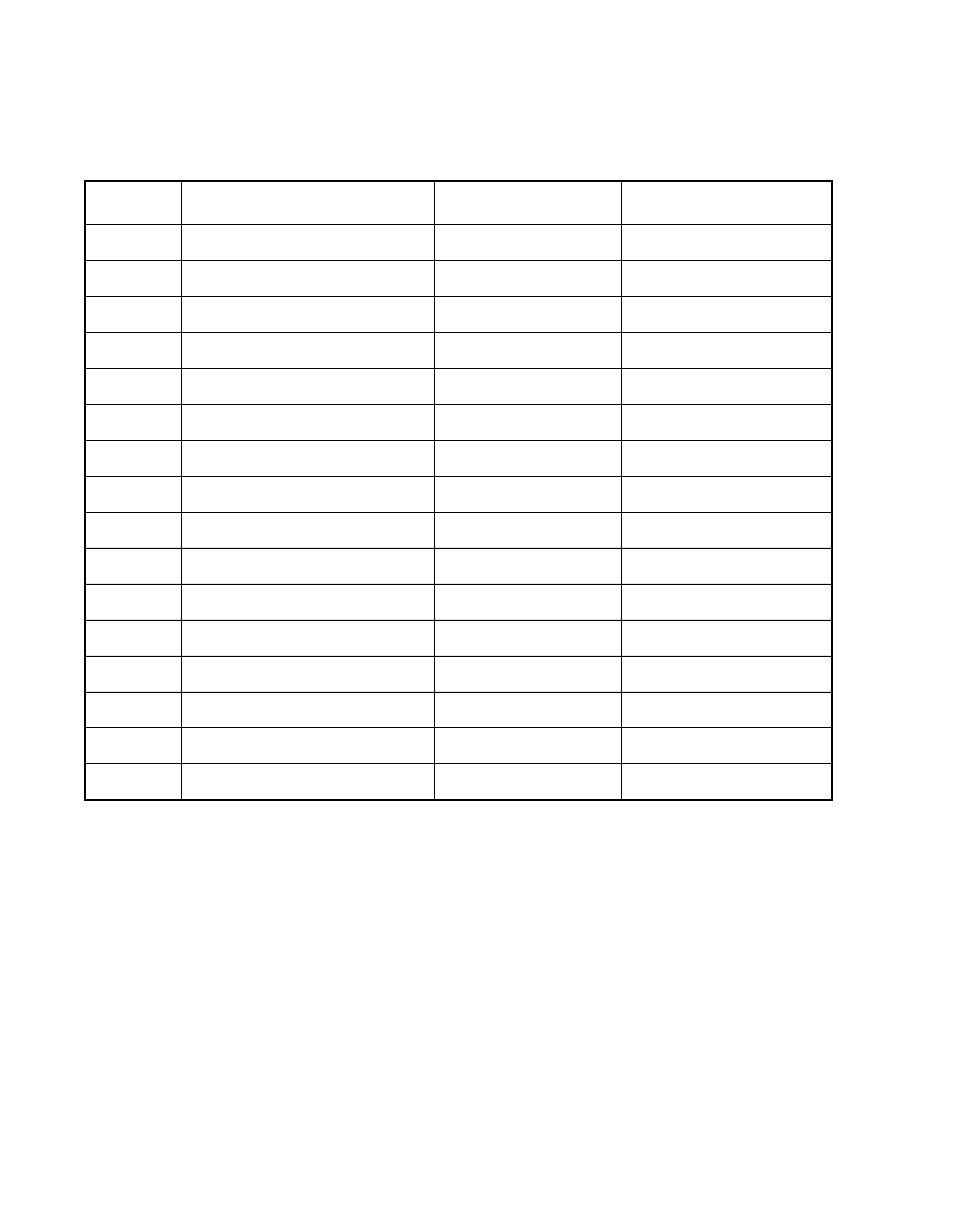

Table 3.1

PCI Bus Commands and Encoding Types

C_BE[3:0] Command Type

Supported as Master Supported as Slave

0000

Special Interrupt Acknowledge

No

No

0001

Special Cycle

No

No

0010

I/O Read Cycle

Yes

Yes

0011

I/O Write Cycle

Yes

Yes

0100

Reserved

N/A

N/A

0101

Reserved

N/A

N/A

0110

Memory Read

Yes

Yes

0111

Memory Write

Yes

Yes

1000

Reserved

N/A

N/A

1001

Reserved

N/A

N/A

1010

Configuration Read

No

Yes

1011

Configuration Write

No

Yes

1100

Memory Read Multiple

Yes

1

No (defaults to 0110)

1101

Dual Address Cycle

No

No

1110

Memory Read Line

Yes

2

No (defaults to 0110)

1111

Memory Write and Invalidate

Yes

3

No (defaults to 0111)

1. This operation is selectable by bit 2 in the

operating register.

2. This operation is selectable by bit 3 in the

operating register.

3. This operation is selectable by bit 0 in the

operating register.