Table 7.21 initiator asynchronous receive, Figure7.32 initiator asynchronous receive, Table 7.22 target asynchronous send – Avago Technologies LSI8751D User Manual

Page 288: Figure7.33 target asynchronous send, Initiator asynchronous receive, Target asynchronous send

7-52

Instruction Set of the I/O Processor

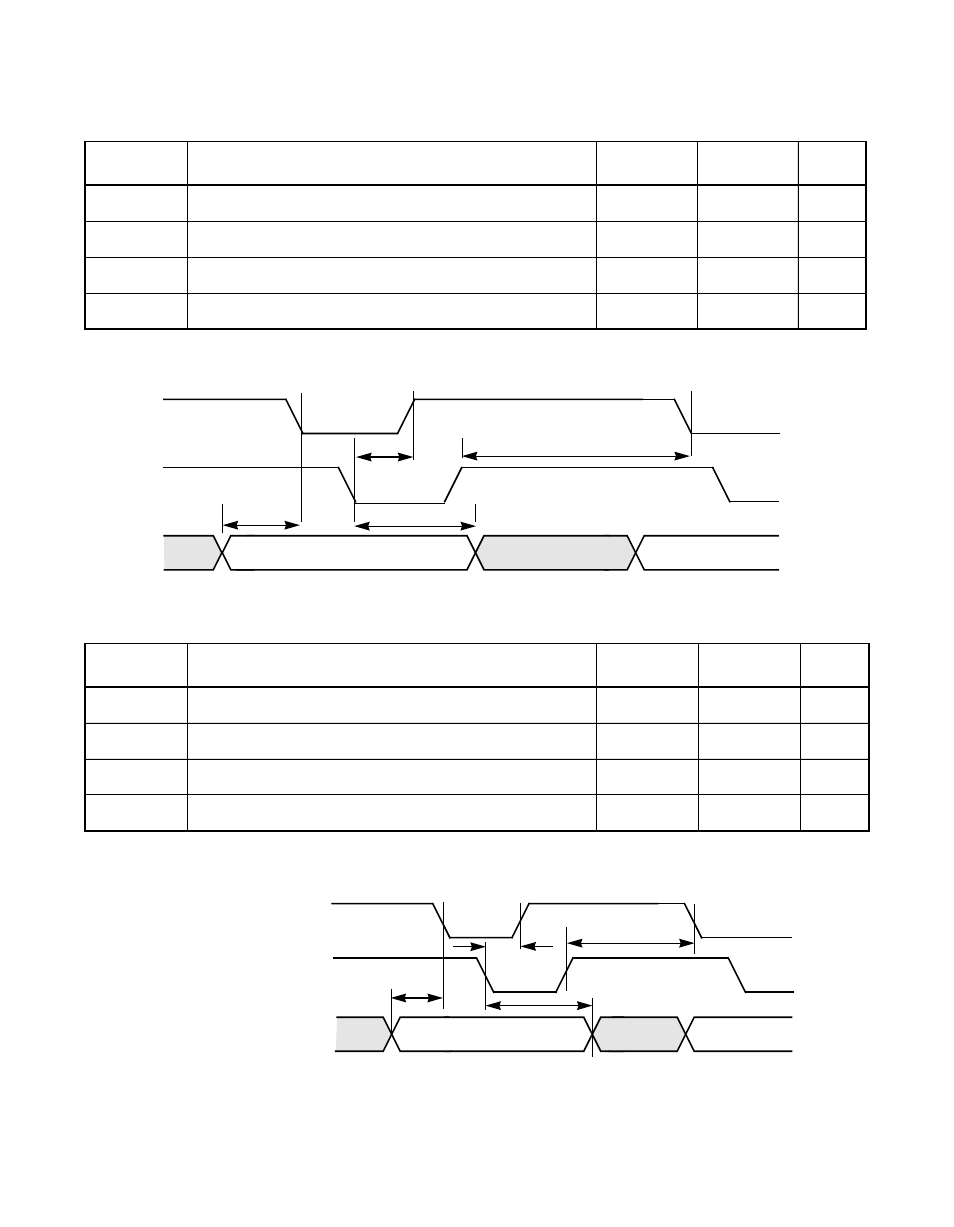

Figure 7.32 Initiator Asynchronous Receive

Figure 7.33 Target Asynchronous Send

Table 7.21

Initiator Asynchronous Receive

Symbol

Parameter

Min

Max

Unit

t

1

SACK/ asserted from SREQ/ asserted

5

–

ns

t

2

SACK/ deasserted from SREQ/ deasserted

5

–

ns

t

3

Data setup to SREQ/ asserted

0

–

ns

t

4

Data hold from SACK/ asserted

0

–

ns

Table 7.22

Target Asynchronous Send

Symbol

Parameter

Min

Max

Unit

t

1

SREQ/ deasserted from SACK/ asserted

5

–

ns

t

2

SREQ/ asserted from SACK/ deasserted

5

–

ns

t

3

Data setup to SREQ/ asserted

55

–

ns

t

4

Data hold from SACK/ asserted

20

–

ns

SREQ/

SACK/

SD[15:0]/,

SDP[1:0]/

t

1

t

2

n + 1

Valid n + 1

Valid n

n

t

3

t

4

n

n + 1

Valid n

Valid n + 1

n + 1

n + 1

n

n

t

1

t

2

t

3

t

4

SREQ/

SACK/

SD[15:0]/,

SDP[1:0]/

This manual is related to the following products: