Table 4.6 interface control signals, Interface control signals – Avago Technologies LSI8751D User Manual

Page 104

4-12

Signal Descriptions

describes the Interface Control Signals group.

PAR

LSI53C875,

LSI53C875J: 25

LSI53C875N: 31

LSI53C875JB: H1

T/S

Parity is the even parity bit that protects the AD[31:0]

and C_BE[3:0]/ lines. During address phase, both the

address and command bits are covered. During data

phase, both data and byte enables are covered.

BYTEPAR[3:0]

(LSI53C875N

only)

193, 8, 34, 47

T/S

When the PCI Byte Parity pins are enabled, the

LSI53C875N checks each byte of incoming data on the

PCI bus against its corresponding parity line, in

addition to the normal parity checking against the PCI

PAR signal. This extra parity checking/generation is

always enabled for the LSI53C875N. Is not register

selectable. A parity error on any Byte Parity pin for PCI

master read or slave write operation causes a fatal

DMA interrupt and SCRIPTS stops running. Mask this

interrupt with the Extended Byte Parity Enable bit, bit 1

of the

register.

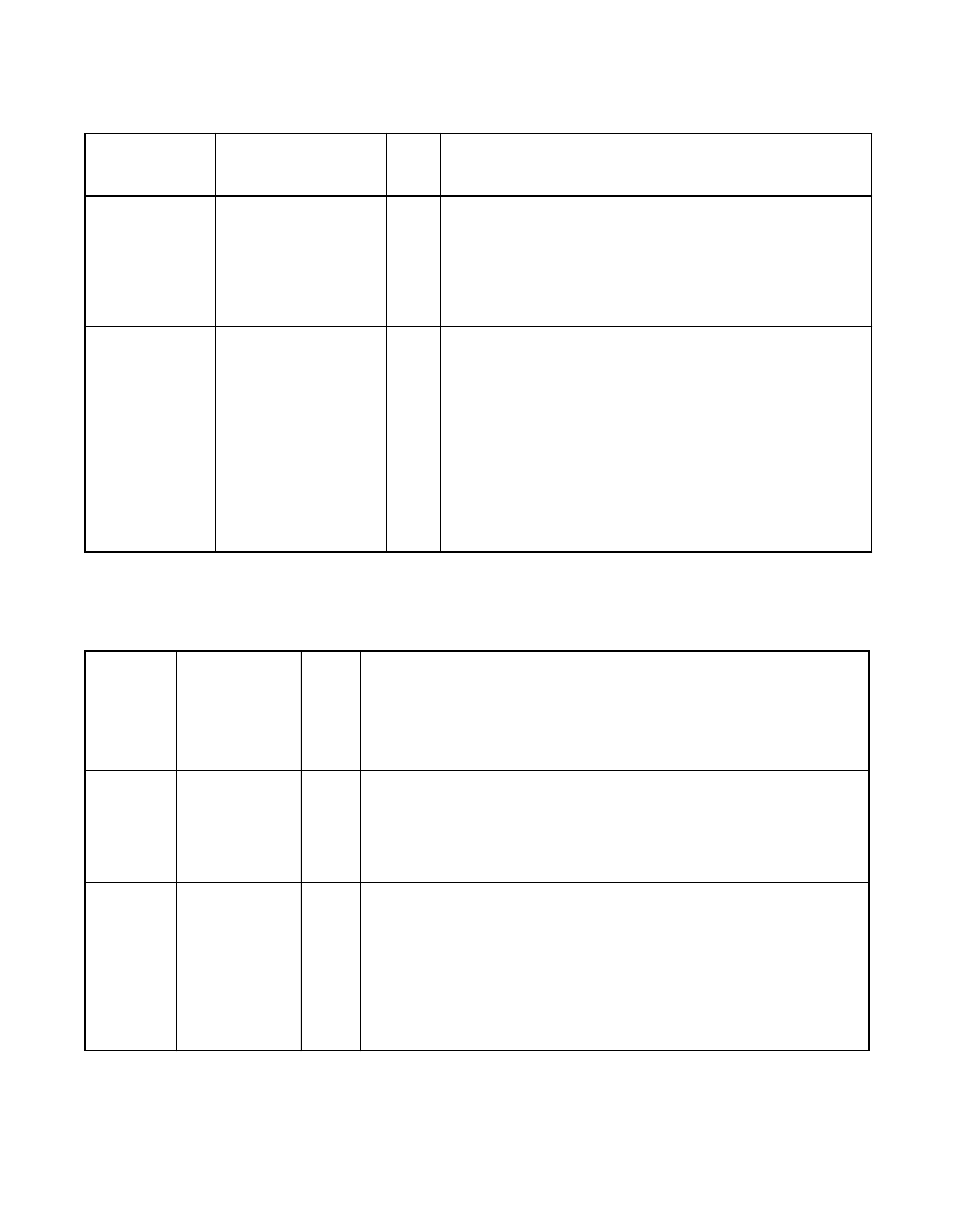

Table 4.5

Address and Data Signals (Cont.)

Name

Pin No.

Typ

e

Description

Table 4.6

Interface Control Signals

Name

Pin No.

LSI53C875,

LSI53C875J,

LSI53C875N,

LSI53C875JB

Type

Description

FRAME/

16/22/F2

S/T/S

Cycle Frame is driven by the current master to indicate the

beginning and duration of an access. FRAME/ is asserted to

indicate a bus transaction is beginning. While FRAME/ is

asserted, data transfers continue. When FRAME/ is deasserted,

the transaction is in the final data phase or the bus is idle.

TRDY/

19/25/G3

S/T/S

Target Ready indicates the target agent’s (selected device’s)

ability to complete the current data phase of the transaction.

TRDY/ is used with IRDY/. A data phase is completed on any

clock when both TRDY/ and IRDY/ are sampled asserted. During

a read, TRDY/ indicates that valid data is present on AD[31:0].

During a write, it indicates the target is prepared to accept data.

Wait cycles are inserted until both IRDY/ and TRDY/ are asserted

together.