General purpose pin control (gpcntl), General purpose pin control, Gpcntl) – Avago Technologies LSI8751D User Manual

Page 179

5-63

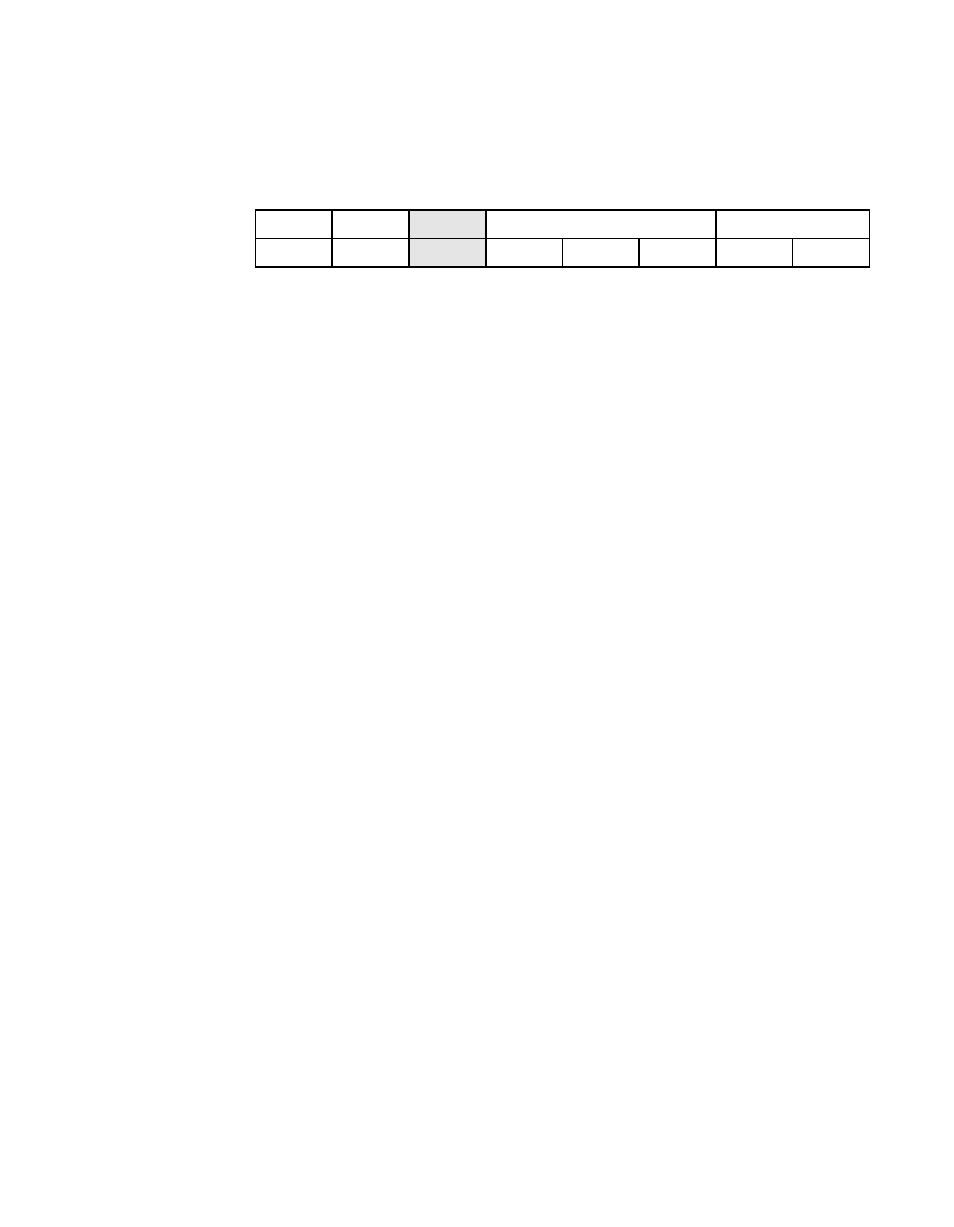

Register: 0x47 (0xC7)

General Purpose Pin Control (GPCNTL)

Read/Write

This register is used to determine if the pins controlled by the

register are inputs or outputs. Bits [4:0] in GPCNTL

correspond to bits [4:0] in the

register. When

the bits are enabled as inputs, an internal pull-up is also enabled.

ME

Master Enable

7

The internal bus master signal is presented on GPIO1 if

this bit is set, regardless of the state of bit 1 (GPIO1_EN).

FE

Fetch Enable

6

The internal opcode fetch signal is presented on GPIO0

if this bit is set, regardless of the state of bit 0

(GPIO0_EN).

R

Reserved

5

GPIO4_EN[4:2]

GPIO Enable

[4:2]

The General purpose control, corresponding to bits [4:2]

in the

register and pins 60,

59, and 57. GPIO4 powers up as a general purpose

output, and GPIO[3:2] power-up as general purpose

inputs.

GPIO1_EN[1:0]

GPIO Enable

[1:0]

These bits power-up set, causing the GPIO1 and GPIO0

pins to become inputs. Clearing these bits causes

GPIO[1:0] to become outputs.

7

6

5

4

2

1

0

ME

FE

R

GPIO

GPIO

0

0

x

0

1

1

1

1