Avago Technologies LSI8751D User Manual

Page 111

4-19

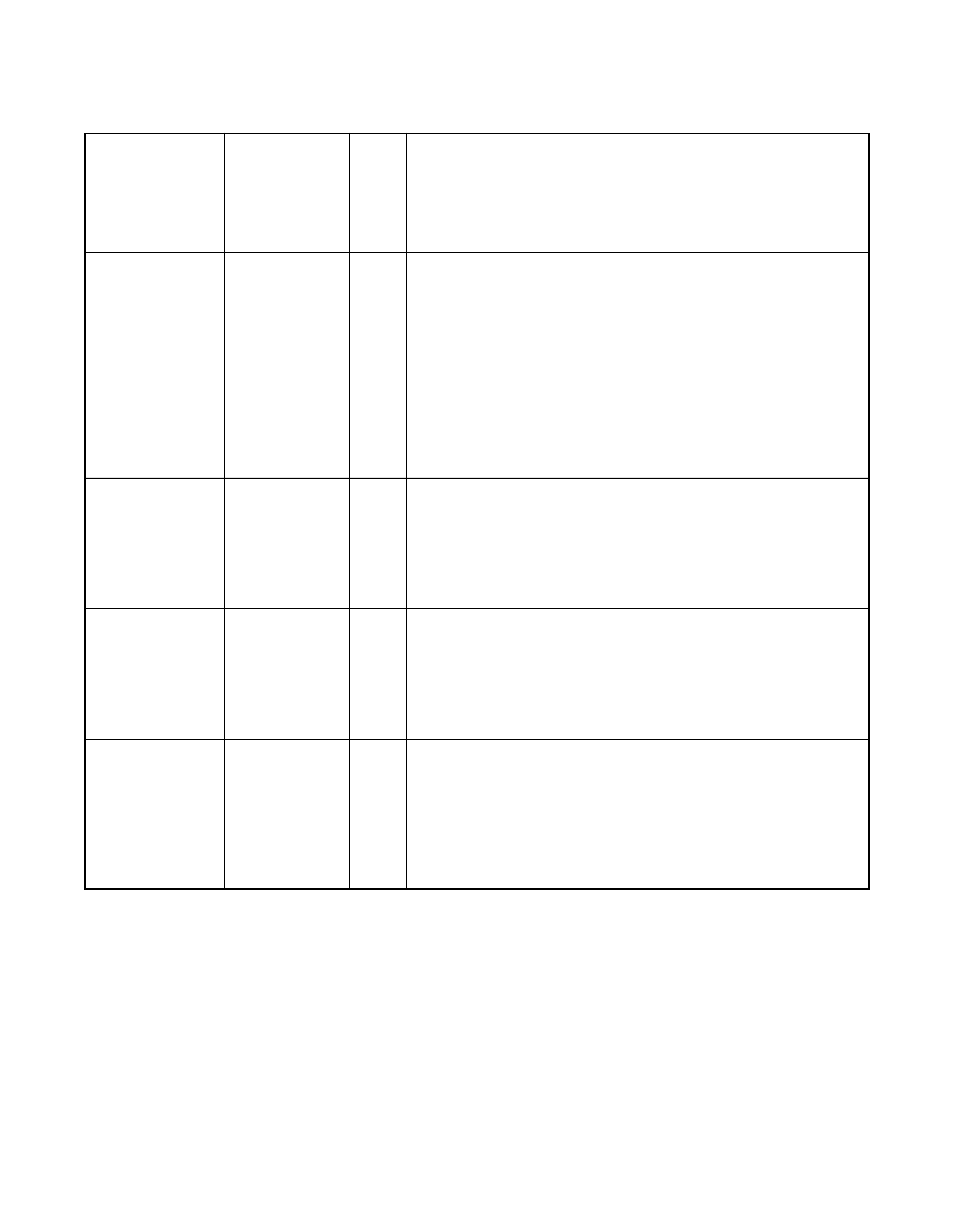

GPIO[4:3]

71, 70/90,

89/L9, M9

I/O

General Purpose I/O pins. GPIO4 powers up as an output.

It can be used as the enable line for V

PP

, the 12 V power

supply to the external Flash memory interface. GPIO3

powers up as an input.

LSI Logic SDMS software uses GPIO3 to detect a

differential board. If the pin is pulled LOW externally, the

board is configured by SDMS software as a differential

board. If it is pulled HIGH or left floating, SDMS software

configures it as an SE board. The LSI Logic PCI to SCSI

host adapters use the GPIO4 pin in the process of flashing

a new SDMS software ROM.

DIFFSENS

72/91/H8

I

The Differential Sense pin detects the presence of an SE

device on a differential system. When external differential

transceivers are used and a zero is detected on this pin, all

chip SCSI outputs will be 3-stated to avoid damage to the

transceivers. This pin should be tied HIGH during SE

operation. The normal value of this pin is 1.

MAC/_

TESTOUT (Not

available on

LSI53C875,

LSI53C875JB)

58, NA/76/NA

T/S

Memory Access Control. This pin can be programmed to

indicate local or system memory accesses (non-PCI

applications). It is also used to test the connectivity of the

LSI53C875 signals using an “AND tree” scheme. The

MAC/_TESTOUT pin is only driven as the Test Out

function when the TESTIN/ pin is driven LOW.

IRQ/

52/69/M5

O

Interrupt. This signal, when asserted LOW, indicates that

an interrupting condition has occurred and that service is

required from the host CPU. The output drive of this pin is

programmed as either open drain with an internal weak

pull-up or, optionally, as a totem pole driver. Refer to the

description of

register, bit 3, for

additional information.

Table 4.10

Additional Interface Signals (Cont.)

Name

Pin No.

LSI53C875,

LSI53C875J,

LSI53C875N,

LSI53C875JB

Type

Description