Table 7.6 capacitance, Table 7.7 output signals—mac/_testout, req, Table 7.9 output signal—serr – Avago Technologies LSI8751D User Manual

Page 240: Capacitance, Output signals—mac/_testout, req, Output signal—serr

7-4

Instruction Set of the I/O Processor

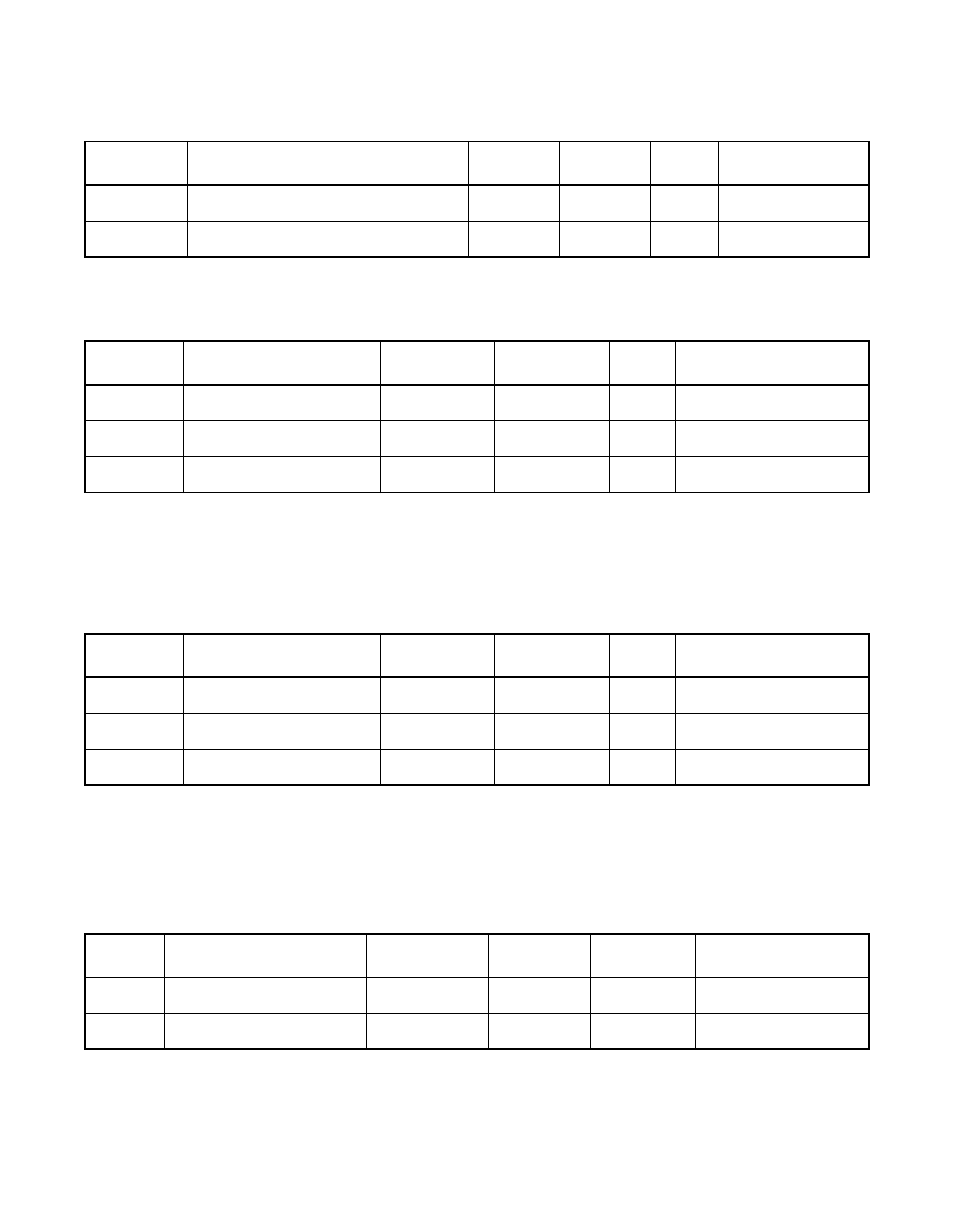

Table 7.6

Capacitance

Symbol

Parameter

Min

Max

Unit

Test Conditions

C

I

Input capacitance of input pads

–

7

pF

–

C

IO

Input capacitance of I/O pads

–

10

pF

–

Table 7.7

Output Signals—MAC/_TESTOUT, REQ/

Symbol

Parameter

Min

Max

Unit

Test Conditions

V

OH

Output high voltage

2.4

V

DD

V

−

16 mA

V

OL

Output low voltage

V

SS

0.4

V

16 mA

I

OZ

3-state leakage

−

10

10

µ

A

–

Note: REQ/ has a 100

µ

A pull-up that is enabled when TESTIN is low.

Table 7.8

Output Signals—IRQ/, SDIR[15:0], SDIRP0, SDIRP1, BSYDIR, SELDIR,

RSTDIR, TGS, IGS, MAS/[1:0], MCE/, MOE/, MWE/

Symbol

Parameter

Min

Max

Unit

Test Conditions

V

OH

Output high voltage

2.4

V

DD

V

−

4 mA

1

1. For IRQ/, Test Conditions are 8 mA.

Note: IRQ/, MAS/[1:0], MCE/, MOE/, and MWE/ have a 100

µ

A pull-up that is enabled when TESTIN

is low. IRQ/ can be enabled with a register as an open drain with an internal 100

µ

A pull-up.

V

OL

Output low voltage

V

SS

0.4

V

4 mA

1

I

OZ

3-state leakage

−

10

10

µ

A

–

Table 7.9

Output Signal—SERR/

Symbol

Parameter

Min

Max

Unit

Test Conditions

V

OL

Output low voltage

V

SS

0.4

V

16 mA

I

OZ

3-state leakage

−

10

10

µ

A

–