Scsi transfer (sxfer), Scsi transfer, Sxfer) – Avago Technologies LSI8751D User Manual

Page 131

5-15

Register: 0x05 (0x85)

SCSI Transfer (SXFER)

Read/Write

Note:

When using Table Indirect I/O commands, bits [7:0] of this

register are loaded from the I/O data structure.

For additional information on how the synchronous transfer rate is

determined, refer to

Chapter 2, “Functional Description.”

TP[2:0]

SCSI Synchronous Transfer Period

[7:5]

These bits determine the SCSI synchronous transfer

period used by the LSI53C875 when sending

synchronous SCSI data in either initiator or target mode.

These bits control the programmable dividers in the chip.

Note:

For Ultra SCSI transfers, the ideal transfer period is 4, and

5 is acceptable. Setting the transfer period to a value

greater than 5 is not recommended.

The synchronous transfer period the LSI53C875 should

use when transferring SCSI data is determined as in this

example.

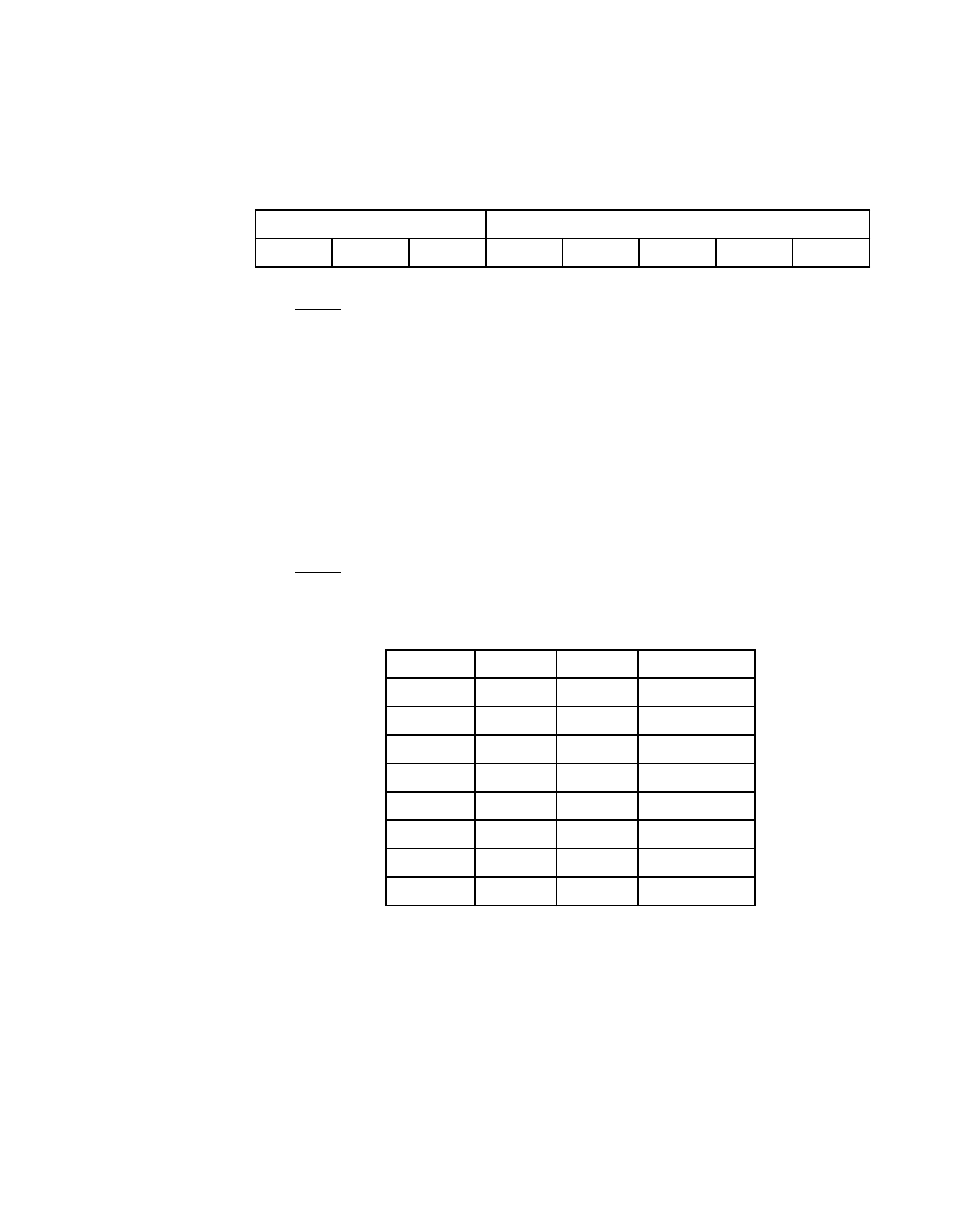

7

5

4

0

TP[2:0]

MO[4:0]

0

0

0

0

0

0

0

0

TP2

TP1

TP0

XFERP

0

0

0

4

0

0

1

5

0

1

0

6

0

1

1

7

1

0

0

8

1

0

1

9

1

1

0

10

1

1

1

11